# Model AV100 Technical Reference Manual

MANUAL NUMBER : 00793-001-1A

http://www.indcompsrc.com

6260 SEQUENCE DRIVE, SAN DIEGO, CA 92121 (619) 677-0877 (FAX) 619-677-0895 INDUSTRIAL COMPUTER SOURCE EUROPE TEL (1) 69.18.74.40 FAX (1) 64.46.40.42 · INDUSTRIAL COMPUTER SOURCE (UK) LTD TEL 01243-533900 FAX 01243-532949

# FORWARD

This product manual provides information to install, operate and or program the referenced product(s) manufactured or distributed by Industrial Computer Source. The following pages contain information regarding the warranty and repair policies.

Technical assistance is available at: 1-800-480-0044.

**Manual Errors, Omissions and Bugs:** A "Bug Sheet" is included as the last page of this manual. Please use the "Bug Sheet" if you experience any problems with the manual that requires correction.

## NOTE

The information in this document is provided for *reference* only. Industrial Computer Source does not assume any liability arising out of the application or use of the information or products described herein. This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Industrial Computer Source, nor the rights of others.

Copyright © 1995 by Industrial Computer Source, a California Corporation, 6260 Sequence Drive, San Diego, CA 92121. Industrial Computer Source is a Registered Trademark of Industrial Computer Source. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

This page intentionally left blank

# Guarantee

A thirty day money-back guarantee is provided on all **standard** products sold. **Special order products** are covered by our Limited Warranty, *however they may not be returned for refund or credit*.

### Refunds

In order to receive a full refund on a product purchase price, the product must not have been damaged by the customer or by the common carrier chosen by the customer to return the goods, and the product must be returned complete (meaning all manuals, software, cables, etc.) within 30 days of receipt and in as-new and resalable condition. The **Return Procedure** must be followed to assure prompt refund.

# **Restocking Charges**

Product returned *after* 30 days, and *before* 90 days, of the purchase will be subject to a **minimum** 20% restocking charge and any charges for damaged or missing parts.

Products not returned within 90 days of purchase, or products which are not in as-new and resaleable condition, are not eligible for credit return and will be returned to the customer.

# **Limited Warranty**

One year limited warranty on all products sold with the exception of the "Performance Series" I/O products, which are warranted to the original purchaser, for as long as they own the product, subject to all other conditions below, including those regarding neglect, misuse and acts of God. Within one year of purchase, Industrial Computer Source will repair or replace, at our option, any defective product. At any time after one year, we will repair or replace, at our option, any defective "Performance Series" I/O product sold. This does not include products damaged in shipment, or damaged through customer neglect or misuse. Industrial Computer Source will service the warranty for all standard catalog products for the first year from the date of shipment. After the first year, for products not manufactured by Industrial Computer Source, the remainder of the manufacturer's warranty, if any, will be serviced by the manufacturer directly.

The **Return Procedure** must be followed to assure repair or replacement. Industrial Computer Source will normally return your replacement or repaired item via UPS Blue. *Overnight delivery or delivery via other carriers is available at additional charge*.

The limited warranty is void if the product has been subjected to alteration, neglect, misuse, or abuse; if any repairs have been attempted by anyone other than Industrial Computer Source or its authorized agent; or if the failure is caused by accident, acts of God, or other causes beyond the control of Industrial Computer Source or the manufacturer. Neglect, misuse, and abuse shall include any installation, operation, or maintenance of the product other than in accordance with the owners' manual.

No agent, dealer, distributor, service company, or other party is authorized to change, modify, or extend the terms of this Limited Warranty in any manner whatsoever. Industrial Computer Source reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

Shipments not in compliance with this Guarantee and Limited Warranty Return Policy will not be accepted by Industrial Computer Source.

# **Return Procedure**

For any Limited Warranty or Guarantee return, please contact Industrial Computer Source's Customer Service at **1-800-480-0044** and obtain a Return Material Authorization (RMA) Number. All product(s) returned to Industrial Computer Source for service or credit **must** be accompanied by a Return Material Authorization (RMA) Number. Freight on all returned items **must** be prepaid by the customer who is responsible for any loss or damage caused by common carrier in transit. Returns for Warranty **must** include a Failure Report for each unit, by serial number(s), as well as a copy of the original invoice showing date of purchase.

To reduce risk of damage, returns of product must be in an Industrial Computer Source shipping container. If the original container has been lost or damaged, new shipping containers may be obtained from Industrial Computer Source Customer Service at a nominal cost.

# **Limitation of Liability**

In no event shall Industrial Computer Source be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental, or consequential damages in connection with or arising out of the performance or use of any product furnished hereunder. Industrial Computer Source liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by Industrial Computer Source or its authorized agent.

Some *Sales Items* and *Customized Systems* are **not** subject to the guarantee and limited warranty. However in these instances, any deviations will be disclosed prior to sales and noted in the original invoice. *Industrial Computer Source reserves the right to refuse returns or credits on software or special order items.*

| FORWARD                                    |     |

|--------------------------------------------|-----|

| Guarantee                                  |     |

| Limited Warranty                           | v   |

| Return Procedure                           | vi  |

| Limitation of Liability                    | vi  |

| Chapter 1: About This Manual               |     |

| Purpose                                    |     |

| Who Can Use This Manual                    |     |

| Conventions Used In This Manual            | 1-1 |

| Chapter 2: Overview                        | 2-1 |

| Introduction                               |     |

| Possible Applications                      |     |

| Hardware Description                       |     |

| Hardware Component Differences             |     |

| Software Description                       |     |

| Control Program Software                   |     |

| Host Interface Software                    |     |

| Host Support Software                      |     |

| Chapter 3: Host PC Hardware Interface      |     |

| Introduction                               |     |

| Dual Port RAM General Information          |     |

| Avanstar Family ISA Bus Board              |     |

| Avanstar Family EISA Bus Board             |     |

| Chapter 4: Avanstar Family Control Program | 4-1 |

| Introduction                               |     |

| Dual Port RAM Interface                    | 4-1 |

| Global Control Block                       |     |

| Channel Control Blocks                     | 4-9 |

| Buffer Area                                |     |

| Transmitting Characters                    |     |

| Receiving Characters                       |     |

| Communication Errors                       |     |

| Configuring Parameters                     |     |

| Service Requests                           |     |

| Interrupt Handling                         |     |

# **Table of Contents**

| Chapter 5: Reset and Download Procedure      |     |

|----------------------------------------------|-----|

| -<br>Avanstar Reset And Download Procedures  | 5-1 |

| ISA Board Procedures                         | 5-1 |

| EISA Procedures                              | 5-3 |

|                                              |     |

| Chapter 6: MicroProcessor Hardware Interface | 6-1 |

| Chapter 6: MicroProcessor Hardware Interface |     |

| •                                            | 6-1 |

| UART Addressing             | 6-1 |

|-----------------------------|-----|

| Board I/O Registers         | 6-2 |

| ISA Registers               | 6-2 |

| EISA Registers              | 6-3 |

| UART Interrupts             | 6-3 |

| Control Program Development | 6-3 |

# List of Figures

| Figure 2.1 - Avanstar Family Hardware Structure |

|-------------------------------------------------|

|-------------------------------------------------|

# List of Tables

| Table 2.1 - Hardware Component Differences                   | 2-3  |

|--------------------------------------------------------------|------|

| Table 4.1 - Global Control Block Fields                      | 4-2  |

| Table 4.2 - Channel Control Block Default Parameters         | 4-9  |

| Table 4.3 - Control Program Channel Control Block Definition | 4-10 |

| Table 4.4 - Available Baud Rates                             | 4-11 |

# **Current Revision 1A**

October 1995

# **Chapter 1: About This Manual**

# Purpose

This technical reference manual provides technical information needed to write software for the Avanstar (AV100x) family of intelligent communications adapters from Industrial Computer Source.

# Who Can Use This Manual

This manual is designed for users experienced in programming software interfaces between applications programs and communications hardware. A working knowledge of the following topics is assumed:

- Asynchronous communication protocols.

- PC architecture and operation.

# **Conventions Used In This Manual**

This manual uses the following conventions:

- "local RAM" refers to "scratch RAM"

- "map register" refers to "latch register"

- To be consistent with programming usage, ports are numbered from 0 to 15 instead of 1 to 16.

- When discussing the dual port RAM, addresses are referenced relative to the dual port base starting address. This is because dual port RAM can be located in many different areas of memory. For example, if you select D0000H as the starting address of the dual port RAM, then the address of the Global Status Word would actually be D0002H.

- Three different numbering systems appear in this manual: binary, hexadecimal, and decimal. Each numbering system is used in its conventional context.

- Binary notation is used to represent bit values. An example is shown below.

Bit 5 4 3 Parity Type

- x x 0 No Parity

- 0 0 1 Generate and check Odd Parity.

- 0 1 1 Generate and check Even Parity.

- 1 0 1 Generate and check Mark Parity.

- 1 1 1 Generate and check Space Parity.

- Hexadecimal notation is used to identify memory addresses and command codes. Hexadecimal numbers are always followed by "H". For example: 06H, 10H, 0AH.

- Decimal notation is used in its usual context. For example: 4 boards, 3 seconds.

- A cleared bit has a value of 0. A set bit has a value of 1.

- The term "character time" refers to the time required to transmit one character.

This page intentionally left blank

# **Chapter 2: Overview**

# Introduction

The Avanstar family is a line of intelligent communication adapters that add serial ports to ISA and EISA computer systems. Each adapter has an on-board microprocessor to relieve the computer system of much of the processing necessary to support those ports. The family consists of the:

- AV100I Series for the ISA bus.

- AV100E Series for the EISA bus.

These adapters are, for the most part, functionally compatible with one another. Any differences between the adapters will be discussed in this manual.

# **Possible Applications**

The Avanstar family adapters' versatility makes them useful for a wide range of data communication applications. For example, they may be used for data collection, process control, and interfacing to printers, scanners, modems, scales, terminals, bar code readers, burglar alarm sensors and laboratory instrumentation.

With additional programming, an Avanstar family adapter can also:

- Perform line discipline functions such as local terminal emulations and character conversions.

- Perform file-oriented algorithms such as data compacting on an interchannel basis. For example, a file can be received through one port, processed, and then re-transmitted through the same, different, or multiple ports simultaneously.

- Reconcile format differences without host computer intervention. This makes it appear as if one device is directly compatible with another system even though the actual format is different. For example, an intelligent repeater may convert ASCII to EBCDIC.

# **Hardware Description**

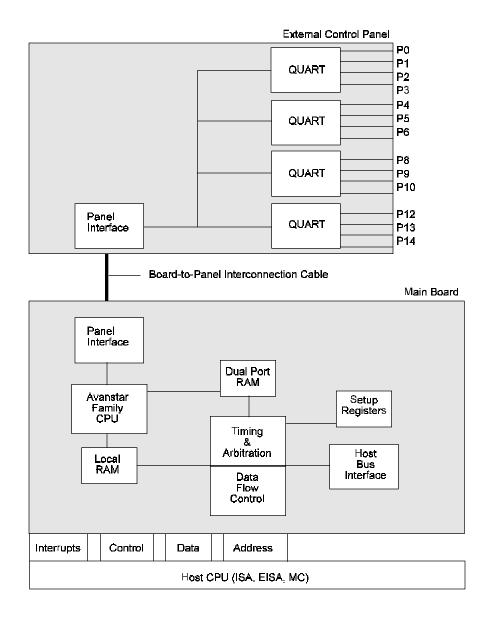

The main hardware components of the Avanstar family boards are the microprocessor, QUARTs, dual ported RAM, and local RAM.

- The microprocessor is the key component of an Avanstar family board. Its main function is to transfer data from the host PC to the QUARTs, and to transfer received data from the QUARTs to the host PC. The other components of an Avanstar family board support this function.

- The QUARTs (Quad Universal Asynchronous Receiver Transmitters) are devices which convert the on-board microprocessor's parallel data into serial data for the EIA-232 interface. QUARTs also receive serial EIA-232 data and convert it to parallel data for the on-board microprocessor.

- The dual port RAM is the interface between the on-board microprocessor and the host PC.

- The local RAM is the storage location for the program that is downloaded from the host PC. The local RAM is also used for temporary data storage.

A functional diagram of the Avanstar family hardware is shown in Figure 2.1.

Figure 2.1 - Avanstar Family Hardware Structure.

# Hardware Component Differences

The basic similarities and differences among the Avanstar family adapters are summarized in the next table. Detailed information about the adapters is given in Chapter 6.

|               |      | Micro         | Dual |

|---------------|------|---------------|------|

| Adapter Type  | Bus  | Processor     | Port |

| Avanstar 100i | ISA  | 80186 (16MHz) | 16K  |

| Avanstar 100e | EISA | 80186 (16MHz) | 32K  |

#### Table 2.1 - Hardware Component Differences

There are five types of external connection panels available for all these adapters:

- 1. 8-port non-configurable panel

- 2. 8-port configurable panel

- 3. 16-port non-configurable panel

- 4. 16-port configurable panel

- 5. 8-channel multi-modem panel

The ports on the 8-port and the 16-port configurable panels can be software-configured as either EIA-232 or EIA-422. See the Line Protocol and Channel Command register descriptions in Chapter 4, section 4.4 for information on doing this. See your driver manual for a description of the utility which will also change the interface type.

# **Software Description**

Three types of software enable the Avanstar family boards to function: (1) control program software, (2) host interface software, and (3) host support software.

#### **Control Program Software**

Control program software is downloaded from the host PC and executed by the on-board microprocessor. Industrial Computer Source provides standard control programs to handle communication for all boards. The information needed to write custom control program software is in Chapter 6.

### Host Interface Software

Host interface software (also known as a device driver) is executed by the host PC. It transfers data from the host to the Avanstar family board, and from the Avanstar family board to the host. Various device drivers are available from Industrial Computer Source. The information needed to write custom host interface software is in Chapters 3 and 4.

# NOTE:

If you are planning to support more than one type of Avanstar family adapter, it is practical to write one piece of host system software to support all types of adapters. Industrial Computer Source typically supports all adapters with the same device driver.

## **Host Support Software**

Host support software, which is executed on the host PC, includes programs for downloading and board configuration. The information needed to write custom host support software is in Chapters 3, 4, and 5. Sample support software is provided by Industrial Computer Source on the Developer's Disk.

# NOTE

If you are planning to support more than one type of Avanstar family adapter, it is practical to write one piece of host system software to support all types of adapters. Industrial Computer Source typically supports all adapters with the same device driver.

# **Chapter 3: Host PC Hardware Interface**

# Introduction

This chapter covers the Avanstar family hardware that can be accessed by the host PC.

# **Dual Port RAM General Information**

The dual port RAM is the interface between the host microprocessor and the on-board microprocessor. This memory is called dual-ported because both microprocessors can access it in order to communicate information between each other.

The dual port RAM's structure and use are determined by the software executing on the on-board microprocessor. The Avanstar family control program uses the structure and protocol defined in Chapter 4 to communicate with the host PC.

# **Avanstar Family ISA Bus Board**

The following are the I/O registers for the ISA board.

## Board ID Register (Read only) Offset:0000H

The first read after a hardware reset will be ECH. The second read will be 13H. The data will toggle between these two values on subsequent reads.

## Control Register 1 Offset:0001H

| 7                          | 6                          | 5 | 4       | 3  | 2                            | 1                                    | 0 |

|----------------------------|----------------------------|---|---------|----|------------------------------|--------------------------------------|---|

| IRQ Enable<br>(Read/Write) | IRQ Select<br>(Read/Write) |   | Not Use | ed | Download Bit<br>(Read/Write) | Program<br>Ready Bit<br>(Read/Write) |   |

All bits are cleared to zero upon an ISA bus reset.

#### Bit 0 Program Ready Bit (Read Only)

This bit is the 80186 program ready indicator. It is cleared upon reset or download. It is set by the 80186 control program after it is downloaded and initialization is completed.

#### Bit 1 Download Bit (Read/Write)

This bit is tied to the 80186 reset line. Writing a one (1) to this position allows the 80186 to start executing instructions. It is usually preferable to do this after the control program has been downloaded.

Bits 6-4 IRQ Select (Read/Write)

These bits determine which ISA interrupt will be driven by the board.

| Bit 6 | 5 | 4 | IRQ |

|-------|---|---|-----|

| 0     | 0 | 0 | 3   |

| 0     | 0 | 1 | 4   |

| 0     | 1 | 0 | 5   |

| 0     | 1 | 1 | 9   |

| 1     | 0 | 0 | 10  |

| 1     | 0 | 1 | 11  |

| 1     | 1 | 0 | 12  |

| 1     | 1 | 1 | 15  |

|       |   |   |     |

Bit 7 IRQ Enable (Read/Write)

This bit is used to enable the selected IRQ to be driven.

# Control Register 2 Offset:0002H

| 7            | 6            | 5    | 4           | 3      | 2           | 1   | 0   |

|--------------|--------------|------|-------------|--------|-------------|-----|-----|

| 186 IRQ      | 186 IRQ      | Not  | Memory      | Memory |             | ,   |     |

| Enable       | Data         | Used | Enable      | B      | Bank Select |     | ect |

| (Read/Write) | (Read/Write) |      | (Read/Write | Bits   |             |     |     |

|              |              |      |             | (R     | ead         | Wri | te) |

All bits are cleared to zero upon an ISA bus reset.

Bits 3-0 Memory Bank Select Bits (Read/Write)

These bits are used to select the correct 16K memory bank from either the dual port or the local RAM as applicable. During download, the two low order bits of this register correspond to the two high order bits of the local RAMs.

#### Bit 4 Memory Enable (Read/Write)

This bit determines if the board responds to any ISA memory cycles. When in download mode, this bit controls the local RAM response to ISA memory cycles. When not in download mode, this bit controls the dual port RAM response to ISA memory cycles.

Bit 6 186 IRQ Data (Read Only)

This bit reflects the current state of the 80186 IRQ data bit which is toggled by the control program. See section 6.5—80186 register PCS1.

## Bit 7 186 IRQ Enable (Read Only)

This bit reflects the current state of the 80186 IRQ enable bit which is toggled by the control program. See section 6.5—80186 register PCS1.

| 7                      | 6                      | 5                      | 4                      | 3                      | 2                      | 1   | 0    |

|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-----|------|

| Address<br>Line<br>A19 | Address<br>Line<br>A18 | Address<br>Line<br>A17 | Address<br>Line<br>A16 | Address<br>Line<br>A15 | Address<br>Line<br>A14 | Not | Used |

#### ISA Bus Dual Port Address Register (R/W) Offset:0003H

All bits are cleared to zero upon an ISA bus reset.

Bits 7-2 Address Lines A19-A14

These bits select address lines A19-A14 for the base address of the dual port RAM 16K byte window.

#### ISA Bus Board Interrupt Status Register 1 Offset:0004H

| 7       | 6      | 5      | 4       | 3       | 2       | 1       | 0       |

|---------|--------|--------|---------|---------|---------|---------|---------|

| Channel | Channe | Channe | Channel | Channel | Channel | Channel | Channel |

| 8       | 7      | 6      | 5       | 4       | 3       | 2       | 1       |

This register gives the pending interrupt status for channels 1-8. The register is read only from the ISA bus and write only from the 80186. The bits are cleared when there is a reset, an ISA bus read, or when the Download Bit in Control Register 1 is low. This register is not used by the standard Avanstar family control program.

#### ISA Bus Board Interrupt Status Register 2 0

Offset:0005H

| 7       | 6      | 5      | 4       | 3       | 2       | 1       | 0       |

|---------|--------|--------|---------|---------|---------|---------|---------|

| Channel | Channe | Channe | Channel | Channel | Channel | Channel | Channel |

| 16      | 15     | 14     | 13      | 12      | 11      | 10      | 9       |

This register gives the pending interrupt status for channels 9-16. The register is read-only from the ISA bus and write-only from the 80186. The bits are cleared when there is a reset, an ISA bus read, or when the Download Bit in Control Register 1 is low. This register is not used by the standard Avanstar family control program.

# **Avanstar Family EISA Bus Board**

The Avanstar EISA board uses EISA slot-specific I/O registers. They are located from xC80H through xCAEH, where x is the EISA slot number in hexadecimal. For example, if an Avanstar EISA board is installed in slot 1, its registers would be located at I/O addresses 1C80H through 1CAEH.

### EISA Bus Board ID Registers (Read only)

Register at I/O Address xC80H

Register at I/O Address xC81H

Register at I/O Address xC82H

| 7 |     | 0 |

|---|-----|---|

|   | 01H | I |

|   |     |   |

Register at I/O Address xC83H

These registers contain the four-byte EISA Board ID.

## **Board Control Register**

I/O Address: xC84H

| 7 | 6  | 5      | 4   | 3 | 2                        | 1                      | 0                      |

|---|----|--------|-----|---|--------------------------|------------------------|------------------------|

|   | Re | served | (0) | I | IOCHKRST<br>(write only) | IOCHKRS<br>(Read only) | ENABLE<br>(Read/Write) |

This register contains the ENABLE, IOCHKERR, and IOCHKRST bits defined in the EISA specification.

Bit 0 Enable (Read/Write)

Setting this bit to 1 enables the board for operation. Clearing this bit to 0 disables operation of the board and causes it to respond only to slot-specific I/O. This bit is cleared to 0 on reset and when the IOCHKRST bit is pulsed.

#### Bit 1 IOCHKERR (Read Only)

This bit is set to 1 to indicate a serious error. This bit is cleared to 0 on reset and when the IOCHKRST bit is pulsed.

#### Bit 2 IOCHKRST (Write Only)

This bit is cleared to 0 for normal operation. Pulse this bit to 1 for at least 500 ns to reset the board. Pulsing this bit disables the board and clears the ENABLE and IOCHKERR bits.

#### Map Registers I/O Addresses: xC85H-xC87H

Register at I/O Address xC85H

| 7                     | 6                      | 5                      | 4                      | 3                      | 2                      | 1           | 0          |

|-----------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------|------------|

| ddress<br>Line<br>A15 | Address<br>Line<br>A14 | Address<br>Line<br>A13 | Address<br>Line<br>A12 | Address<br>Line<br>A11 | Address<br>Line<br>A10 | Always<br>0 | Alway<br>0 |

Register at I/O Address xC86H

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0      |

|---------|---------|---------|---------|---------|---------|---------|--------|

| Address | Addres |

| Line    | Line   |

| A23     | A22     | A21     | A20     | A19     | A18     | A17     | A16    |

Register at I/O Address xC87H

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0      |

|---------|---------|---------|---------|---------|---------|---------|--------|

| Address | Addres |

| Line    | Line   |

| A31     | A30     | A29     | A28     | A27     | A26     | A25     | A24    |

These registers select address lines A31-A10 for the dual port RAM.

#### EISA Bus Board Dual Port Mode Register

7 0 Dual Port Mode

I/O Address: xCA1H

This register determines the mode of operation of the dual port RAM. Before accessing the dual port RAM while in Download Mode, this register must be set to 4EH. Before accessing the dual port RAM in the Normal Operating Mode, this register must be set to 6EH.

#### EISA Bus Board Interrupt Select Register I/O Address: xCA8H

| 7 |           | 0                   |

|---|-----------|---------------------|

|   | Undefined | Interrupt<br>Select |

This register is used in conjunction with the Interrupt Configuration and Status Register to determine which IRQ level the board uses. See the Interrupt Level Bits of the Interrupt Configuration and Status Register for use of this register. The Interrupt Select bit is reset to 0 after a hardware reset.

| 7                    | 6        | 5           | 4           | 3                   | 2        | 1            | 0 |

|----------------------|----------|-------------|-------------|---------------------|----------|--------------|---|

| Interrupt<br>Pending | Reserved | Always<br>0 | Always<br>1 | Interrupt<br>Enable | Reserved | Inter<br>Lev | 1 |

## EISA Bus Board Interrupt Configuration and Status Register I/O Address: xCA9H

This register, in conjunction with the Interrupt Select Register, determines the configuration of interrupts of the board. Reading this register reports the interrupt status of the board and also clears the interrupt. Interrupt service routines must read this register at the start of their processing to clear the interrupt.

Bits 1-0 Interrupt Level

These bits, in conjunction with the Interrupt Select Bit of the Interrupt Select Register, determine which IRQ level the board uses.

# Interrupt Bit

| Select Bit | <u>1</u> | <u>0</u> | IRQ Level |

|------------|----------|----------|-----------|

| 0          | 0        | 0        | IRQ 3     |

| 0          | 0        | 1        | IRQ 4     |

| 0          | 1        | 0        | IRQ 5     |

| 0          | 1        | 1        | IRQ 9     |

| 1          | 0        | 0        | IRQ 10    |

| 1          | 0        | 1        | IRQ 11    |

| 1          | 1        | 0        | IRQ 12    |

| 1          | 1        | 1        | IRQ 15    |

|            |          |          |           |

## Bit 3 Interrupt Enable

Setting this bit to 1 enables interrupts from the board. Clearing this bit to 0 disables interrupts from the board.

## Bit 7 Interrupt Pending

This bit is set to 1 when an interrupt is pending. This bit is cleared to 0 when there is not an interrupt pending. This bit is reset to 0 after this register is read.

# EISA Bus Board Status Register I/O Address: xCACH

| 7 |           | 0              |

|---|-----------|----------------|

|   | Undefined | Board<br>Ready |

|   |           | Ready          |

This register returns the status of the board.

Bit 0 Board Ready

This bit is set to 1 when the processor sets its ready bit. This bit is cleared to 0 when the processor has not set its ready bit. This bit is reset to 0 when the board is placed in reset or in the download mode.

#### EISA Bus Board Download Register I/O Address: xCADH

| 7 |           | 2 | 1                              | 0              |

|---|-----------|---|--------------------------------|----------------|

|   | Undefined |   | Local<br>RAM<br>Bank<br>Select | Board<br>Ready |

This register controls the board mode and selects the local RAM block in the download mode.

#### Bit 0 Download Mode

Clearing this bit to 0 places the board in the download mode. This holds the processor in the reset state and forces the local RAM to overlay the dual port RAM for the download operation. Setting this bit to 1 sets the main board and processor to normal operation.

#### Bit 1 Local RAM Bank Select

The Avanstar EISA board has 64KB of local RAM, but there is only a 32KB window to the host. This bit selects which block of the local RAM is mapped to the host's window.

Clearing this bit to 0 selects the lower local RAM block (0000H - 7FFFH). Setting this bit to 1 selects the upper local RAM block (8000H - FFFFH).

#### EISA Bus Board Dual Port Enable Register I/O Address: xCAEH

7

6

5

4

3

2

1

0

Always 0

Dual Port Enable

Always 0

Always 0

This register enables and disables the dual port RAM.

Bit 4 Dual Port Enable

Setting this bit to 1 enables the dual port RAM. Clearing this bit to 0 disables the dual port RAM.

## NOTE:

Please refer to the Hitachi HD6498IF EISA Slave Interface Controller data sheet ( available from your local Hitachi rep) for a further description of these registers.

This page intentionally left blank

# Chapter 4: Avanstar Family Control Program

# Introduction

The Avanstar family control program is the standard control program software provided by Industrial Computer Source. It contains the code necessary to carry out the main functions of the Avanstar family: transmitting and receiving data.

Each type of Avanstar family adapter has a separate but functionally compatible control program. The following table lists the Avanstar family adapters with their control program filenames.

| Board Type    | Control Program Filename |

|---------------|--------------------------|

| Avanstar 100i | A100I.CP                 |

| Avanstar 100e | A100E.CP                 |

The Avanstar family Developer's disk contains the DOS utility program A100LOAD.EXE that will download a control program to any Avanstar family board. The source code for A100LOAD.EXE is also contained on the Avanstar family developer's disk.

# **Dual Port RAM Interface**

The Avanstar family control program and the host interface program communicate through the dual port RAM. This chapter describes the structure of this interface and its theory of operation.

The Avanstar family control program logically divides the dual port RAM into three sections:

- Global Control Block

- Channel Control Blocks

- Buffer Area

# **Global Control Block**

The Global Control Block (GCB) is the section of the dual port memory which contains command fields and data which apply to the Avanstar family board in general. Table 4.1 lists the fields making up the Global Control Block.

| GCB Offset | Field Description                       | Access |

|------------|-----------------------------------------|--------|

| 0000H      | Global Command Word                     | (R/W)  |

| 0002H      | Global Status Word                      | (RO)   |

| 0004H      | Global Service Request                  | (X)    |

| 0006H      | Available Buffer Space Remaining        | (RO)   |

| 0008H      | Board Type                              | (RO)   |

| 000AH      | Avanstar Family Control Program Version | (RO)   |

| 000CH      | Channel Control Block Count             | (RO)   |

| 000EH      | Channel Control Block Offset            | (RO)   |

| 0010H      | Channel Control Block Size              | (RO)   |

| 0012H      | Global Command Word 2                   | (R/W)  |

| 0014H      | Global Status Word 2                    | (RO)   |

| 0016H      | Communication Error Service Request     | (X)    |

| 0018H      | Input Buffer Service Request            | (X)    |

| 001AH      | Output Buffer Service Request           | (X)    |

| 001CH      | Modem Status Change Service Request     | (X)    |

| 001EH      | Channel Command Service Request         | (X)    |

|            |                                         |        |

TABLE 4.1 - Global Control Block Fields

## NOTES

- 1. Offsets are from the base address of the Global Control Block. The base address of the Global Control Block is the same as the base address that was selected for the dual-port RAM.

- 2. The different access types are:

- (RO) Read Only

- (R/W) Read and Write

- (X) Exchange

The fields with an access type of (X) are Service Request fields.

#### Global Command Word (R/W)

#### GCB Offset: 0000H

The host interface program uses the Global Command Word to issue commands to the Avanstar family control program. Write the desired command to this field, wait for the field to return to 0000H, and then check the Global Status Word for any errors.

#### Global Command 0000H: Ready

After the Avanstar family control program has been downloaded and its initialization has been completed, the program enters the Normal Operating Mode and writes a 0000H to the Global Command Word. In this mode, characters can be transmitted and received, channels can be configured, and commands can be issued to the Avanstar family control program.

#### Global Command 0001H: Diagnostic Mode

Diagnostic Mode is not currently implemented by the Avanstar family control program.

#### Global Command 0002: Reset

Reset stops the Avanstar control program and restarts the resident firmware. This command deletes the Avanstar family control program from the local RAM and prepares the adapter for another download. This is a software-only reset; no hardware is reset by this command.

#### Global Status Word (RO) GCB Offset: 0002H

The host interface uses the Global Status Word to find out the current status of the Avanstar family control program and related hardware.

#### Global Status 0000H: Ready

Ready means that the Avanstar family control program is in the Normal Operating Mode and that no errors have occurred.

#### Global Status 0001H: Stopped

Stopped means that the Avanstar family control program has stopped because of an unexpected error.

### Global Status 0002: Dual Port RAM Error

Dual Port RAM Error means that the Avanstar family control program detected an error in the dual port memory during initialization.

#### Global Status 0003H: Invalid Command

Invalid Command means that an invalid command was placed in the Global Command Word.

#### Global Status 0004H: Busy

Busy is placed in the Status Word by the Avanstar family control program while it is initializing. After it has initialized, the Avanstar family control program enters the Normal Operating Mode and places a 0000H in the Status Word to indicate that it is ready.

## Global Service Request (X) GCB Offset: 0004H

| 7             | 6            | 5            | 4             | 3             | 2             | 1            | 0            |

|---------------|--------------|--------------|---------------|---------------|---------------|--------------|--------------|

| Channel<br>7  | Channe<br>6  | Channe<br>5  | Channel<br>4  | Channel<br>3  | Channel<br>2  | Channel<br>1 | Channel<br>0 |

|               |              |              |               |               |               |              |              |

| 15            | 14           | 13           | 12            | 11            | 10            | 9            | 8            |

| Channel<br>15 | Channe<br>14 | Channe<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>9 | Channel<br>8 |

The Global Service Request is used to indicate the channels which request service. Each time any of the five service request conditions occur, the bit corresponding to the channel is set.

For all eight-port boards, bits 15-8 are always cleared to 0.

## Available Buffer Space Remaining (RO) GCB Offset: 0006H

This field shows the amount of buffer space available for input and output buffers. The Available Buffer Space Remaining field is updated after each configuration.

# Board Type (RO) GCB Offset: 0008H

| Value | Board Type    |

|-------|---------------|

| 0006H | Avanstar 100m |

| 000AH | Avanstar 100e |

| 000CH | Avanstar x00i |

### Avanstar Control Program Version (RO) GCB Offset: 000AH

| 7  | Hex Digit 1 | 4  | 3  | Hex Digit 0 | 0 |

|----|-------------|----|----|-------------|---|

| 15 | Hex Digit 3 | 12 | 11 | Hex Digit 2 | 8 |

This field shows the Avanstar family control program version in use. The version level is encoded into the field as follows: version WX.YX is encoded as WXYZH, where W, X, Y and Z represent hexadecimal digits. For example, version 4.56 would be encoded as 0456H.

### Channel Control Block Count (RO) GCB Offset: 000CH

This field shows the number of channel control blocks set up by the control program. This number reflects the number of ports (8 or 16) on the external connection panel.

### Channel Control Block Offset (RO) GCB Offset: 000EH

This field contains the offset of the first Channel Control Block (CCB) from the base of the dual ported memory. This is necessary because future revisions may change the size of the GCB. Use this field to determine the base address of the first CCB.

## Channel Control Block Size (RO) GCB Offset: 0010H

This field contains the size of each Channel Control Block (CCB). This is necessary because future revisions may change the size of the CCB. Use this field to determine the base addresses of the remaining CCBs.

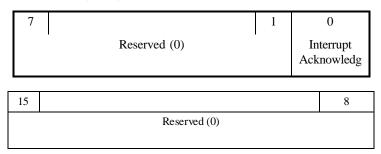

### Global Command Word 2 (R/W) GCB Offset: 0012H

The Global Command Word 2 is used by the application to give additional commands to the control program.

#### Bit 0 Interrupt Acknowledge

Setting this bit to "1" informs the Avanstar family control program that the host interface program is ready to accept interrupts. This bit is set only once.

#### Global Status Word 2 (RO) GCB Offset: 0014H

| 7               |    | 6          |                  | 3              |    | 2                          |               |                      | 1               | 0                    |  |

|-----------------|----|------------|------------------|----------------|----|----------------------------|---------------|----------------------|-----------------|----------------------|--|

| On-Boa<br>RJ11s | rd | I          | Not Used         | ot Used        |    | Modem<br>Panel<br>Attached |               | EIA-422<br>Available |                 | EIA-232<br>Available |  |

| 15<br>No        |    | 14<br>Jsed | 13<br>Has<br>RTS | 12<br>Ha<br>C1 | as | 11<br>Has<br>DSR           | 1<br>Ha<br>DT | as                   | 9<br>Has<br>DCD | 8<br>Has<br>RI       |  |

|                 |    |            | K15              | CI             | 3  | DSK                        |               | . N                  | DCD             | KI                   |  |

The Global Status Word 2 field contains a unique ID which describes what type of external connection panel is installed. The ID is read by the control program at power-up and is made available to the driver.

## NOTE:

A value of 0000H in this field indicates either that no external connection panel is installed, or a non-Avanstar family external connection panel is installed.

Bit 7 On-Board RJ11s

This board has RJ type connectors on it-no panel is attached.

Bits 8-13

This adapter supports the indicated handshake signals. (1=supported)

|    | 7             |                 | 6            |                     | 5             | 4             | 3                | 2             | 1            |            | 0          |   |

|----|---------------|-----------------|--------------|---------------------|---------------|---------------|------------------|---------------|--------------|------------|------------|---|

| Ch | annel<br>7    | el Channel<br>6 |              | Channel Channel 5 4 |               | Channel<br>3  | hannel Channel 2 |               | nel          | Chani<br>0 | nel        |   |

|    |               |                 |              |                     |               |               |                  |               |              |            |            | I |

|    | 15            |                 | 14           |                     | 13            | 12            | 11               | 10            | 9            |            | 8          |   |

|    | Channel<br>15 |                 | Channe<br>14 | el                  | Channel<br>13 | Channel<br>12 | Channel<br>11    | Channel<br>10 | Channel<br>9 | Ch         | annel<br>8 |   |

Communication Error Service Request (X)

GCB Offset: 0016H

This field is used to inform the host interface program which channels require servicing due to communication errors. The bit corresponding to the requesting channel is set each time a break is received or an overrun error, parity error, or framing error occurs.

For all eight-port boards, bits 15-8 are always cleared to 0.

| Input Buffer Service Request (X) | GCB Offset: 0018H |

|----------------------------------|-------------------|

|----------------------------------|-------------------|

|    | 7           |              | 6     |    | 5            | 4            | 3            | 2            | 1          | (        | )         |

|----|-------------|--------------|-------|----|--------------|--------------|--------------|--------------|------------|----------|-----------|

| Ch | nannel<br>7 | el Channel 6 |       | С  | Thannel<br>5 | Channel<br>4 | Channel<br>3 | Channel<br>2 | Chann<br>1 | iel Char | nnel<br>) |

|    | 15          |              | 14    |    | 13           | 12           | 11           | 10           | 9          | 8        | 7         |

|    | Channel     |              | Chann | el | Channel      | Channel      |              | Channel      | Channel    | Channel  |           |

|    | 15          |              | 14    |    | 13           | 12           | 11           | 10           | 9          | 8        |           |

This field is used to inform the host interface program which channels require servicing due to an input buffer condition. The bit corresponding to the requesting channel is set each time one of these conditions occur:

- The number of characters specified by the trigger rate has been received.

- The most recent character was received more than 4 character times in the past.

- The input buffer fills up.

For all eight-port boards, bits 15-8 are always cleared to 0.

#### Output Buffer Service Request (X)GCB Offset: 001AH

|   | 7             | 6             | 5             | 4             | 3             | 2             | 1            | 0            |

|---|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|

|   | Channel<br>7  | Channel<br>6  | Channel 5     | Channel 4     | Channel 3     | Channel 2     | Channel<br>1 | Channel<br>0 |

| - |               |               |               |               |               |               |              |              |

|   | 15            | 14            | 13            | 12            | 11            | 10            | 9            | 8            |

|   | Channel<br>15 | Channel<br>14 | Channel<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>9 | Channel<br>8 |

This field is used to inform the application program which channels require servicing due to an output buffer condition. The bit corresponding to the requesting channel is set each time the output buffer is empty or at the low water mark.

For all eight-port boards, bits 15-8 are always cleared to 0.

Modem Status Change Service Request (X)

15

9

8

| 7          |        | 6           | 5            | 4            | 3            | 2         | 1          | 0            |     |

|------------|--------|-------------|--------------|--------------|--------------|-----------|------------|--------------|-----|

| Chann<br>7 | el Cl  | hannel<br>6 | Channel<br>5 | Channel<br>4 | Channel<br>3 | Channel 2 | Chann<br>1 | el Chan<br>0 | nel |

|            |        |             |              |              |              |           |            |              | _   |

|            | 15     | 14          | 13           | 12           | 11           | 10        | 9          | 8            |     |

| C          | nannel | Channe      | l Channel    | Channel      | Channel      | Channel   | Channel    | Channel      |     |

12

This field is used to inform the application program which channels require servicing due to a modem status change. The bit corresponding to the requesting channel is set each time the modem status changes.

11

10

For all eight-port boards, bits 15-8 are always cleared to 0.

14

Channel Command Service Request (X) GCB Offset: 001EH

13

| 7             | 6            | 5            | 4             | 3             | 2             | 1            | 0            |

|---------------|--------------|--------------|---------------|---------------|---------------|--------------|--------------|

| Channel<br>7  | Channe<br>6  | Channe<br>5  | Channel<br>4  | Channel<br>3  | Channel<br>2  | Channel<br>1 | Channel<br>0 |

|               |              |              |               |               |               |              |              |

| 15            | 14           | 13           | 12            | 11            | 10            | 9            | 8            |

| Channel<br>15 | Channe<br>14 | Channe<br>13 | Channel<br>12 | Channel<br>11 | Channel<br>10 | Channel<br>9 | Channel<br>8 |

This field is used to inform the application program which channels require servicing due to the completion of a channel command. The bit corresponding to the requesting channel is set each time a channel command is completed successfully or unsuccessfully.

For all eight-port boards, bits 15-8 are always cleared to 0.

# **Channel Control Blocks**

The Channel Control Blocks (CCB) are subdivided into fields which reflect the status of a particular channel. CCBs contain channel-specific data and command words. Certain CCB fields can cause the Avanstar family board to perform specific operations. There is one CCB for each of the channels supported by the board.

Since future revisions of the Avanstar family control program may enlarge the size of the GCB or CCBs, we have devised a method to make upgrading the control program easier. Currently defined fields will always remain fixed relative to the base of their control blocks. Any field added in the future will be added after the current ones.

In the GCB, the Channel Control Block Offset field contains the offset of the first Channel Control Block from the base of the dual port RAM. Use this field to determine the base address of the first CCB. The Channel Control Block Count field of the GCB contains the number of Channel Control Blocks set up by the Avanstar family control program.

The Channel Control Block Size field of the GCB contains the size of each Channel Control Block. Use this field to determine the base addresses of the remaining CCBs.

After downloading, a set of default configuration parameters is established. The CCB default parameter values are:

|     | Baud Rate              | 9600    |                                |

|-----|------------------------|---------|--------------------------------|

|     | Bits Per Character     | 8       |                                |

|     | Number of Stop Bits    | 1       |                                |

|     | Parity Type            | None    |                                |

|     | Line Protocol          | None    |                                |

|     | Input or Output        | 976     | Avanstar 100e (16 ports)       |

|     | Buffer Size            | 2000    | Avanstar 100e (8 ports)        |

|     |                        | 464     | Avanstar 100m, x00i (16 ports) |

|     |                        | 976     | Avanstar 100m, x00i (8 ports)  |

| Inp | ut Buffer Trigger Rate | 0 (Even | ry Character)                  |

| Ou  | tput Buffer Low Water  | 0 (Emp  | oty)                           |

| Inp | ut Buffer High Water   | 944     | Avanstar 100e (16 ports)       |

|     |                        | 1968    | Avanstar 100e (8 ports)        |

|     |                        | 432     | Avanstar 100m, x00i (16 ports) |

|     |                        | 944     | Avanstar 100m, x00i (8 ports)  |

| Inp | ut Buffer Low Water    | 912     | Avanstar 100e (16 ports)       |

|     |                        | 1936    | Avanstar 100e (8 ports)        |

|     |                        | 400     | Avanstar 100m, x00i (16 ports) |

|     |                        | 912     | Avanstar 100m, x00i (8 ports)  |

|     |                        |         |                                |

| CCB Offset | Field Description                 | Access |

|------------|-----------------------------------|--------|

| 0000H      | Baud Rate                         | (R/W)  |

| 0002H      | Data Format                       | (R/W)  |

| 0004H      | Line Protocol                     | (R/W)  |

| 0006H      | Input Buffer Size                 | (R/W)  |

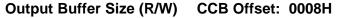

| 0008H      | Output Buffer Size                | R/W)   |

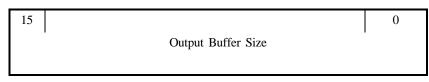

| 000AH      | Input Buffer Trigger Rate         | (R/W)  |

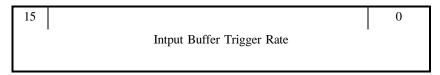

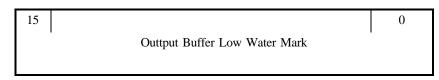

| 000CH      | Output Buffer Low Water Mark      | (R/W)  |

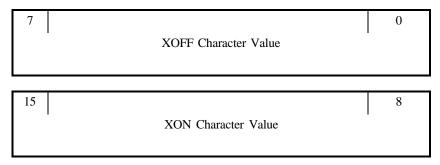

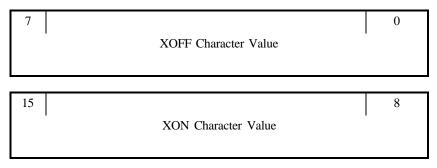

| 000EH      | IXON Characters                   | (R/W)  |

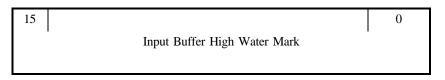

| 0010H      | Input Buffer High Water Mark      | (R/W)  |

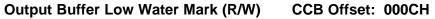

| 0012H      | Input Buffer Low Water Mark       | (R/W)  |

| 0014H      | Channel Command                   | (R/W)  |

| 0016H      | Channel Status                    | (R/W)  |

| 0018H      | Input Buffer Starting Address     | (RO)   |

| 001AH      | Input Buffer Ending Address       | (RO)   |

| 001CH      | Output Buffer Starting Address    | (RO)   |

| 001EH      | Output Buffer Ending Address      | (RO)   |

| 0020H      | Next Character to Input Buffer    | (RO)   |

| 0022H      | Next Character from Input Buffer  | (R/W)  |

| 0024H      | Next Character to Output Buffer   | (R/W)  |

| 0026H      | Next Character from Output Buffer | (RO)   |

| 0028H      | Communication Error Status        | (X)    |

| 002AH      | Bad Character Pointer             | (R/W)  |

| 002CH      | Modem Control                     | (R/W)  |

| 002EH      | Modem Status                      | (RO)   |

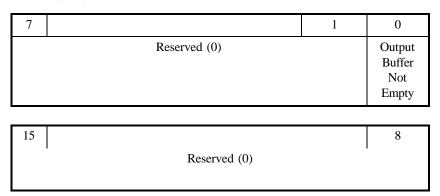

| 0030H      | Blocking Status                   | (RO)   |

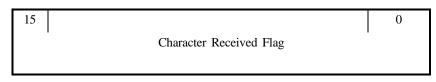

| 0032H      | Character Received Flag           | (R/W)  |

| 0034H      | IXOFF Characters                  | (R/W)  |

| 0036H      | Channel Status 2                  | (RO)   |

TABLE 4.3 - Control Program Channel Control Block Definition

## NOTES

- 1. Offsets are from the base of the specific Channel Control Block.

- 2. The different access types are:

| (RO)  | Read Only      |

|-------|----------------|

| (R/W) | Read and Write |

| (X)   | Exchange       |

The field with an access type of (X) is the Communication Error Status field. This field must be updated by both the host PC and the Avanstar family processor. To avoid the possibility of losing a Communication Error Status bit, the host PC must access and clear the field using the XCHG (assembler) instruction with the register operand cleared to zero.

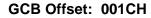

#### Baud Rate (R/W) CCB Offset: 0000H

This field defines a baud rate for the receiver and transmitter in the corresponding Avanstar family board channel.

The following baud rates can be selected on each channel for all Avanstar family boards:

| 50    | 300  | 4800  | 57600  |

|-------|------|-------|--------|

| 75    | 600  | 7200  | 64000  |

| 110   | 1050 | 9600  | 76800  |

| 134.5 | 1200 | 19200 | 115200 |

| 150   | 1800 | 38400 |        |

| 200   | 2400 | 56000 |        |

TABLE 4.4 - Available Baud Rates

### NOTES

- 1. Because decimal values can not be directly represented in the Baud Rate field, it is necessary to use the value 134 in the field in order to program the baud rate 134.5.

- 2. Because the baud rate is stored as an unsigned word value in this field, the highest value that can be represented directly is 65535. Due to this limitation, it is necessary for the control program to perform a translation for some of the higher baud rates. Use the following table to program higher baud rates:

| Actual Baud Rate | Baud Rate Field Value in CCB |

|------------------|------------------------------|

| 76800            | FF00H                        |

| 115200           | FF01H                        |

| 7  | 6            | 5           | 4 | 3 | 2                         | 1                   | 0 |  |

|----|--------------|-------------|---|---|---------------------------|---------------------|---|--|

|    | nnel<br>ode  | Parity Type |   |   | Number<br>of Stop<br>Bits | Number of Data Bits |   |  |

| 15 |              |             |   | б |                           | 9                   | 8 |  |

| 15 | Reserved (0) |             |   |   | Error Repo                | _                   |   |  |

Data Format (R/W) CCB Offset: 0002H

This field defines the number of data bits, number of stop bits, parity type, and channel mode of the corresponding channel.

Bits 1-0 Number of Data Bits

Defines the number of data bits in each transmitted or received character.

| Bit 10 Number of Data Bir |

|---------------------------|

|---------------------------|

- 00 5 Bits

- 0 1 6 Bits

- 10 7 Bits

- 11 8 Bits

Bit 2 Number of Stop Bits

Clearing to "0" generates and checks 1 stop bit. Setting "1" generates and checks 2 stop bits.

Bits 5-3 Parity Type

Defines the parity generated and checked.

- Bit 543 Parity Type

- x x 0 No Parity

- 0 0 1 Generate and Check Odd Parity

- 011 Generate and Check Even Parity

- 101 Generate and Check Mark Parity

- 1 1 1 Generate and Check Space Parity

Bits 7-6 Channel Mode

Each channel can operate in one of four modes.

- Bit 7 6 Mode

- 0.0 Normal

- 0 1 Automatic Echo (Not supported on Avanstar 100m)

- 10 Local Loopback

- 1 1 Remote Loopback

- In the Normal mode, the transmitter and receiver operate independently.

- In the Automatic Echo mode, received data is retransmitted. Received data is sent to the Avanstar family processor, but the Avanstar family CPU-to-transmitter link is disabled.

- In the Local Loopback mode, the transmitter is internally connected to the receiver. The transmitter output is held in the mark state.

- In the Remote Loopback mode, received data is retransmitted. Received data is not sent to the Avanstar family processor, and the Avanstar family CPU-to-transmitter link is disabled.

Bit 8 Error Reporting Type

Clearing this bit to 0 causes the control program to report communication errors and to place a value of FFH in the dual port input buffer as described in section 4.5.3. Setting this bit to 1 causes the control program to report communication errors and to place the actual character received in the dual port input buffer as described in section 4.5.3.

#### Bits 15-9 Reserved (0)

These bits are always cleared to 0.

#### Line Protocol (R/W) CCB Offset: 0004H

| 7              | 6        | 5           | 4        | 3           | 2     | 1     | 0    |

|----------------|----------|-------------|----------|-------------|-------|-------|------|

| Enable         | Input    | Transmitter | Receiver | CTS         | IXOFF | IXANY | IXON |

| Modem          | Buffer   | Controls    | Controls | Controls    |       |       |      |

| Control/Status | Controls | RTS         | DTR      | Transmitter |       |       |      |

|                | RTS      |             |          |             |       |       |      |

| Γ | 15     | 14      | 13                | 12                        | 11 | 10     | 9       | 8 |

|---|--------|---------|-------------------|---------------------------|----|--------|---------|---|

|   | Reserv | red (0) | Interface<br>Type | Character Strip<br>Enable |    | Reserv | ved (0) | ) |

This field defines the line protocol used for the UART.

#### Bit 0 IXON

This bit enables start/stop output control. When the Avanstar family adapter receives the XOFF character, it stops sending data on that channel until the XON character is received. Then transmission is resumed.

To select the XON/XOFF characters for control, place the hex codes of the desired characters in the upper and lower byte of the IXON Characters field of the CCB.

#### Bit 1 IXANY

Use of this protocol requires that IXON also be enabled. When the Avanstar family adapter receives the XOFF character, it stops sending data on that channel. Once transmission is suspended, any character received on that channel will cause character transmission to resume if this bit is set.

As with the IXON protocol, place the XON/XOFF characters used for control in the IXON Characters field. If none are specified, the default is XON = 11H and XOFF = 13H.

### Bit 2 IXOFF

Setting this bit transmits start/stop characters. When the input buffer reaches the mark set by the Input Buffer High Water Mark field, the character defined as XOFF is transmitted. This signals the remote device to stop sending characters. After the input buffer level is emptied to below the value set by the Input Buffer Low Water Mark, the character defined as XON is transmitted. This signals the remote device to resume sending characters.

To select the XON/XOFF characters for control, place the hex codes of the desired characters in the upper and lower byte of the IXOFF Characters field. If none are specified, the default is XON = 11H and XOFF = 13H.

### Bit 3 CTS Controls Transmitter

Setting this bit specifies that the transmitter will respond to the state of the CTS handshake line. This function is implemented in the UART hardware. When the CTS line is asserted, the transmitter is enabled to transmit characters. When the CTS line is negated, the transmitter is disabled and will not transmit any characters.

### Bit 4 Receiver Controls DTR

Setting this bit specifies that the UART hardware controls the DTR line. DTR is always asserted, except when the UART input FIFO fills up. The blocking status is not updated by this protocol.

If Modem Control/Status is enabled, the DTR bit in the Modem Control field of the CCB must be set for this protocol to assert DTR.

# NOTE

It may appear that the receiver controls RTS instead of DTR. However, this is only because the external connection panel's RTS and DTR lines have been switched.

#### Bit 5 Transmitter Controls RTS

Setting this bit specifies that the transmitter will control the RTS handshake line. Setting this bit causes the RTS line to be negated automatically one bit time after the characters in both the transmitter shift register and the holding register are completely transmitted.

Bit 6 Input Buffer Controls RTS

Setting this bit specifies that the receiver will control the RTS handshake line. When this protocol is active, the Avanstar family control program will assert the RTS line until the Input Buffer High Water Mark is reached. At that time the RTS line will be negated. The RTS line will be asserted once again only after the number of characters in the input buffer falls below the Input Buffer Low Water Mark. This protocol is implemented in the Avanstar family control program. The blocking status is updated when this protocol is used.

#### Bit 7 Enable Modem Control/Status

Setting this bit makes the following functions available through the dual port:

- Direct control of the DTR and RTS handshake lines.

- Ability to send Break streams.

- Ability to read the status of the CTS, DSR, RI, and DCD handshake lines.

These capabilities are provided through the use of the Modem Control and the Modem Status fields of the CCB.

#### Bit 13 Interface Type

The device driver communicates with the control program through this bit in order to select the interface type. A "1" in this bit selects EIA-422; a "0" selects EIA-232. After this bit has been set or cleared, bit 0 or bit 1 of the appropriate Channel Command field must be set in order to change the interface type.

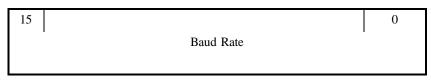

## Input Buffer Size (R/W) CCB Offset: 0006H

This field determines the number of bytes of the dual port RAM allocated for receiving characters. A minimum value of 0002H is required to use a channel; the upper bound is limited only by the amount of dual port RAM available. The value of this field should not be changed while any channel is transmitting or receiving data because characters will be lost.

This field determines the number of bytes of the dual port RAM allocated for transmitting characters. A minimum value of 0002H is required to use a channel; the upper bound is limited only by the amount of dual port RAM available. The value of this field should not be changed while any channel is transmitting or receiving data because characters will be lost.

#### Input Buffer Trigger Rate (R/W) CCB Offset: 000AH

This field defines the number of characters that must be received before the host PC is alerted to a service request. A service request will also be indicated if any characters were received and the most recent character was received more than four character times in the past. The maximum value is 32767.

If interrupts from the Avanstar family board are disabled, the Input Buffer Service Request word of the GCB will still be updated. A value of 0 will indicate a service request on each character received.

This field defines the number of characters that must be left in the output buffer for the host PC to be alerted to a service request. If interrupts from the Avanstar family are disabled, the Output Buffer Service Request field of the GCB will still be updated.

# IXON Characters (R/W) CCB Offset: 000EH

When IXON is enabled in the Line Protocol field, the IXON Characters field determines the characters that, when received, start or stop output. These values are used in conjunction with the IXON and IXANY protocols described earlier in the Line Protocol field description. If both bytes are zero, the default XON (11H) and XOFF (13H) values are used.

# Input Buffer High Water Mark (R/W) CCB Offset: 0010H

This field defines the number of characters that need to be in the input buffer for an XOFF to be transmitted (IXOFF line protocol) or for RTS to be negated (Input Buffer Controls RTS line protocol). This value must be less than the Input Buffer Size.

If both the Input Buffer High Water Mark and Low Water Mark are zero, this value defaults to 32 characters less than the Input Buffer Size.

Input Buffer Low Water Mark (R/W) CCB Offset: 0012H

| 15 |                             | 0 |

|----|-----------------------------|---|

|    | Input Buffer Low Water Mark | · |

This field defines the number of characters that need to be left in the input buffer for an XON to be transmitted (IXOFF line protocol) or for RTS to be asserted (Input Buffer Controls RTS line protocol). This value must be less than the Input Buffer High Water Mark value.

If both the Input Buffer High Water Mark and Low Water Mark are zero, this value defaults to 64 characters less than the Input Buffer Size.

Channel Command (R/W) CCB Offset: 0014H

| 7                      | 6                     | 5                   | 4                  | 3                         | 2                        | 1                                  | 0                                |

|------------------------|-----------------------|---------------------|--------------------|---------------------------|--------------------------|------------------------------------|----------------------------------|

| Disable<br>Transmitter | Enable<br>Transmitter | Disable<br>Receiver | Enable<br>Receiver | Flush<br>Output<br>Buffer | Flush<br>Input<br>Buffer | Configure<br>Channel (not<br>UART) | Configure<br>Channel and<br>UART |

| 15 |              | 10 | 9              | 8        |

|----|--------------|----|----------------|----------|

|    | Reserved (0) |    | Reset<br>Modem | Always 0 |

Setting one or multiple bits in this field to "1" sends the specified commands to the Avanstar family control program. The Avanstar family control program will then perform the commands specified on the channel, write a status value into the Channel Status field, and write a 0000H into the Channel Command field.

Bit 0 Configure Channel and UART

Setting this bit causes these parameters to be configured:

- Baud Rate

- Data Format

- Line Protocol

- Input Buffer Size

- Output Buffer Size

- IXON Characters

- Output Buffer Low Water Mark

- Input Buffer Trigger Rate

- Input Buffer High Water Mark

- Input Buffer Low Water Mark

- Modem Control

- IXOFF Characters

- Interface Type

This command does not reset the input and output buffer pointers unless either buffer size changes. In this case, both pointers on every channel are reset. The Modem Control field is read, and the Modem Control Lines are set accordingly when this command is issued.

## Bit 1 Configure Channel (Not UART)

Setting this bit causes these parameters to be configured:

- Input Buffer Size

- Output Buffer Size

- IXON Characters

- Output Buffer Low Water Mark

- Input Buffer Trigger Rate

- Input Buffer High Water Mark

- Input Buffer Low Water Mark

- Modem Control

- IXOFF Characters

- Interface Type

This command does not reset the input and output buffer pointers unless either buffer size changes. In this case, both pointers on every channel are reset.

The Modem Control field is read, and the Modem Control Lines are set accordingly when this command is issued.

#### Bit 2 Flush Input Buffer

Setting this bit causes both input buffer pointers to be set to the Input Buffer Starting Address.

## Bit 3 Flush Output Buffer

Setting this bit causes both output buffer pointers to be set to the Output Buffer Starting Address.

#### Bit 4 Enable Receiver

Setting this bit causes this channel's receiver to be enabled. This allows it to receive characters.

#### Bit 5 Disable Receiver

Setting this bit causes this channel's receiver to be disabled. This inhibits it from receiving any characters.

#### Bit 6 Enable Transmitter

Setting this bit causes this channel's transmitter to be enabled. This allows it to send characters.

#### Bit 7 Disable Transmitter

Setting this bit causes this channel's transmitter to be disabled. This inhibits it from sending any characters.

#### Bit 9 Reset Modem

If a modem panel is attached, setting this bit causes the channel's modem to execute a hardware reset.

# Channel Status (R/W) CCB Offset: 0016H

This field reports the status of the last command which was executed by setting bits in the Channel Command field.

Possible values are:

| Value | Definition                           |

|-------|--------------------------------------|

| 0000H | No Error                             |

| 0001H | Invalid Baud Rate                    |

| 0002H | Invalid Data Format                  |

| 0003H | Invalid Line Protocol                |

| 0004H | Invalid Input Buffer Size            |

| 0005H | Invalid Output Buffer Size           |

| 0006H | Invalid Input Buffer Trigger Rate    |

| 0007H | Invalid Output Buffer Low Water Mark |

| 0008H | Invalid XON/XOFF Characters          |

| 0009H | Invalid Input Buffer High Water Mark |

| 000AH | Invalid Input Buffer Low Water Mark  |

| 000BH | Non-functional UART                  |

|       |                                      |

## Input Buffer Starting Address (RO) CCB Offset: 0018H

15 Input Buffer Starting Address

This field contains the address of the start of the input buffer. This address is relative to the base of the dual port.

# Input Buffer Ending Address (RO) CCB Offset: 001AH

This field contains the address of the end of the input buffer. This address is relative to the base of the dual port.

## Output Buffer Starting Address (RO) CCB Offset: 001CH

This field contains the address of the start of the output buffer. This address is relative to the base of the dual port.

## Output Buffer Ending Address (RO)

CCB Offset: 001Eh

This field contains the address of the end of the output buffer. This address is relative to the base of the dual port.

# Next Character to Input Buffer (RO) CCB Offset: 0020H

This field contains the address of the next available space in the input buffer. This address is relative to the base address of the dual port. Each time the Avanstar family adapter receives a character, it is placed at this location, and this pointer is incremented by one.

The input buffer is a circular buffer. When the pointer reaches the end of the buffer, the next character will be wrapped around to the start. The Avanstar family control program performs this task automatically.

#### Next Character from Input Buffer (R/W) CCB Offset: 0022H

This field contains the address of the next character to be read from the input buffer. This address is relative to the base address of the dual port. The host interface program must increment this pointer after reading the character in the input buffer. When this pointer reaches the end of the input buffer, it must be wrapped around to the start by the host interface program.

This pointer should always be logically at or behind the Next Character to Input Buffer. When the two pointers are equal, there are no characters in the input buffer.

#### Next Character to Output Buffer (R/W) CCB Offset: 0024H

This field contains the address of the next available space in the output buffer. This address is relative to the base address of the dual port. The host interface program must increment this pointer after placing a character in the output buffer.

This pointer should always be logically at or ahead of the Next Character from Output Buffer. When the two pointers are equal, there are no characters in the output buffer. When the Next Character to Output Buffer pointer reaches the end of the Output Buffer, it must be wrapped around to the start by the host interface program. The host interface program must make sure that this pointer does not wrap around and overtake the Next Character from Output Buffer pointer because this will cause characters to be lost.

#### Next Character from Output Buffer (RO) CCB Offset: 0026H

This field contains the address of the next character to be read from the output buffer. This address is relative to the base of the dual port. The Avanstar family control program increments this pointer after reading the character from the output buffer. Also, the Avanstar family control program will wrap the pointer around to the start when it reaches the end of the output buffer.

| 7 6 5 4      | 3                 | 2                | 1               | 0                |  |  |  |  |  |

|--------------|-------------------|------------------|-----------------|------------------|--|--|--|--|--|

| Reserved (0) | Break<br>Received | Framing<br>Error | Parity<br>Error | Overrun<br>Error |  |  |  |  |  |

| 1.5          |                   |                  |                 |                  |  |  |  |  |  |

| 15           |                   |                  |                 | 8                |  |  |  |  |  |

| Reserved (0) |                   |                  |                 |                  |  |  |  |  |  |

|              |                   |                  |                 |                  |  |  |  |  |  |

## Communication Error Status (X) CCB Offset: 0028H

This field contains a bit pattern of all of the communication errors which have occurred since the last time the application cleared it.

# Bad Character Pointer (R/W) CCB Offset: 002AH

This field contains the address of the first occurrence of an error in the input buffer. This address is relative to the base address of the dual port. After reading this field, the host interface program should reset it to zero. The Avanstar family control program will not update this field unless it has been cleared to zero.

Modem Control (R/W)

#### CCB Offset: 002CH

| 7  | 6       | 5   | 4                       | 3       | 2      | 1                                 | 0                                 |

|----|---------|-----|-------------------------|---------|--------|-----------------------------------|-----------------------------------|

| Re | eserved | (0) | Break<br>(0=of<br>1=on) | Reserve | ed (0) | RTS<br>(o=negated,<br>1=asserted) | DTR<br>(o=negated,<br>1=asserted) |

When the Modem Control/Status bit of the Line Protocol field is set, the Avanstar family control program continually monitors the Modem Control field. Any change to this field will be immediately acted upon. This field is also read and used when a Configure Channel command (Bit 0 or 1 of the Channel Command field) is executed.

The break bit is a one-shot bit. Setting this bit causes a break of a fixed length to be sent. The control program clears this bit after initiating the break.

| 7            | 6 | 5 | 4 | 3                                 | 2                             | 1                                 | 0                                 |

|--------------|---|---|---|-----------------------------------|-------------------------------|-----------------------------------|-----------------------------------|

| Reserved (0) |   |   |   | DCD<br>(o=negated,<br>1=asserted) | RI<br>(o=negate<br>1=asserted | DSR<br>(o=negated,<br>1=asserted) | CTS<br>(o=negated,<br>1=asserted) |

| 1.           | 8 |   |   |                                   |                               |                                   |                                   |