# Model ISA/PCI BACKPLANE Product Manual

MANUAL NUMBER: 00431-020-3A

9950 BARNES CANYON ROAD, SAN DIEGO, CA 92121-2720 (619) 677-0877 (FAX) 619-677-0895 INDUSTRIAL COMPUTER SOURCE EUROPE TEL 01.69.18.74.30 FAX 01.64.46.40.42 • INDUSTRIAL COMPUTER SOURCE (UK) LTD TEL 01243-523500 FAX 01243-532949

## FOREWARD

This product manual provides information to install, operate and or program the referenced product(s) manufactured or distributed by Industrial Computer Source. The following pages contain information regarding the warranty and repair policies.

Technical assistance is available at: 1-800-480-0044.

**Manual Errors, Omissions and Bugs:** A "Bug Sheet" is included as the last page of this manual. Please use the "Bug Sheet" if you experience any problems with the manual that requires correction.

The information in this document is provided for *reference* only. Industrial Computer Source does not assume any liability arising from the application or use of the information or products described herein. This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Industrial Computer Source, nor the rights of others.

Copyright © 1997 by Industrial Computer Source, a California Corporation, 9950 Barnes Canyon Rd., San Diego, CA 92121. Industrial Computer Source is a Registered Trademark of Industrial Computer Source. All trademarks and registered trademarks are the property of their respective owners. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording , or otherwise, without the prior written permission of the publisher.

## Guarantee

A thirty day money-back guarantee is provided on all **standard** products sold. **Special order products** are covered by our Limited Warranty, <u>however they may not be returned for refund or credit</u>. EPROMs, RAM, Flash EPROMs or other forms of solid electronic media are not returnable for credit - but for replacement only. Extended Warranty available. Consult factory.

#### Refunds

In order to receive refund on a product purchase price, the product must not have been damaged by the customer or by the common carrier chosen by the customer to return the goods, and the product must be returned complete (meaning all manuals, software, cables, etc.) within 30 days of receipt and in as-new and resalable condition. The **Return Procedure** must be followed to assure prompt refund.

#### **Restocking Charges**

Product returned *after* 30 days, and *before* 90 days, of the purchase will be subject to a **minimum** 20% restocking charge and any charges for damaged or missing parts.

Products not returned within 90 days of purchase, or products which are not in as-new and resaleable condition, are not eligible for credit return and will be returned to the customer.

## **Limited Warranty**

One-year limited warranty on all products sold with the exception of the "Performance Series" I/O products, which are warranted to the original purchaser for as long as they own the product, subject to all other conditions below, including those regarding neglect, misuse and acts of God. Within one year of purchase, Industrial Computer Source will repair or replace, at our option, any defective product. At any time after one year, we will repair or replace, at our option, any defective "Performance Series" I/O product sold. This does not include products damaged in shipment, or damaged through customer neglect or misuse. Industrial Computer Source will service the warranty for all standard catalog products for the first year from the date of shipment. After the first year, for products not manufactured by Industrial Computer Source, the remainder of the manufacturer's warranty, if any, will be serviced by the manufacturer directly.

The **Return Procedure** must be followed to assure repair or replacement. Industrial Computer Source will normally return your replacement or repaired item via UPS Blue. *Overnight delivery or delivery via other carriers is available at additional charge*.

The limited warranty is void if the product has been subjected to alteration, neglect, misuse, or abuse; if any repairs have been attempted by anyone other than Industrial Computer Source or its authorized agent; or if the failure is caused by accident, acts of God, or other causes beyond the control of Industrial Computer Source or the manufacturer. Neglect, misuse, and abuse shall include any installation, operation, or maintenance of the product other than in accordance with the owners' manual.

No agent, dealer, distributor, service company, or other party is authorized to change, modify, or extend the terms of this Limited Warranty in any manner whatsoever. Industrial Computer Source reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

Shipments not in compliance with this Guarantee and Limited Warranty Return Policy will not be accepted by Industrial Computer Source.

## **Return Procedure**

For any Limited Warranty or Guarantee return, please contact Industrial Computer Source's Customer Service at **1-800-480-0044** and obtain a Return Material Authorization (RMA) Number. All product(s) returned to Industrial Computer Source for service or credit **must** be accompanied by a Return Material Authorization (RMA) Number. Freight on all returned items **must** be prepaid by the customer who is responsible for any loss or damage caused by common carrier in transit. Returns for Warranty **must** include a Failure Report for each unit, by serial number(s), as well as a copy of the original invoice showing date of purchase.

To reduce risk of damage, returns of product must be in an Industrial Computer Source shipping container. If the original container has been lost or damaged, new shipping containers may be obtained from Industrial Computer Source Customer Service at a nominal cost.

## **Limitation of Liability**

In no event shall Industrial Computer Source be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental, or consequential damages in connection with or arising out of the performance or use of any product furnished hereunder. Industrial Computer Source liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by Industrial Computer Source or its authorized agent.

Some *Sales Items* and *Customized Systems* are **not** subject to the guarantee and limited warranty. However, in these instances any deviations will be disclosed prior to sales and noted in the original invoice. *Industrial Computer Source reserves the right to refuse returns or credits on software or special order items*.

## Advisories

Three types of advisories are used throughout the manual to stress important points or warn of potential hazards to the user or the system. They are the Note, the Caution, and the Warning. Following is an example of each type of advisory:

**Note:** The note is used to present special instruction, or to provide extra information which may help to simplify the use of the product.

## CAUTION!

A Caution is used to alert you to a situation which if ignored may cause injury or damage equipment.

## WARNING!

A Warning is used to alert you of a situation which if ignored will cause serious injury.

Cautions and Warnings are accented with triangular symbols. The exclamation symbol is used in all cautions and warnings to help alert you to the important instructions. The lightning flash symbol is used on the left hand side of a caution or a warning if the advisory relates to the presence of voltage which may be of sufficient magnitude to cause electrical shock.

Use caution when servicing any electrical component. We have tried to identify the areas which may pose a Caution or Warning condition in this manual; however, Industrial Computer Source does not claim to have covered all situations which might require the use of a Caution or Warning.

You must refer to the documentation for any component you install into a computer system to insure proper precautions and procedures are followed.

## **Table of Contents**

| FOREWARD                                                                                                                                                                                                                                                                                                                                                                                                                                                | iii                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Guarantee                                                                                                                                                                                                                                                                                                                                                                                                                                               | iv                                                                                                              |

| Limited Warranty                                                                                                                                                                                                                                                                                                                                                                                                                                        | iv                                                                                                              |

| Return Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

| Limitation of Liability                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |

| Advisories                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1_1                                                                                                             |

| Backplane Construction                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                 |

| Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

| Input Power                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |

| ISA BUS Termination                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                 |

| Resistor Termination                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                 |

| RC Network Termination                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                 |

| DIODE Termination                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |

| Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

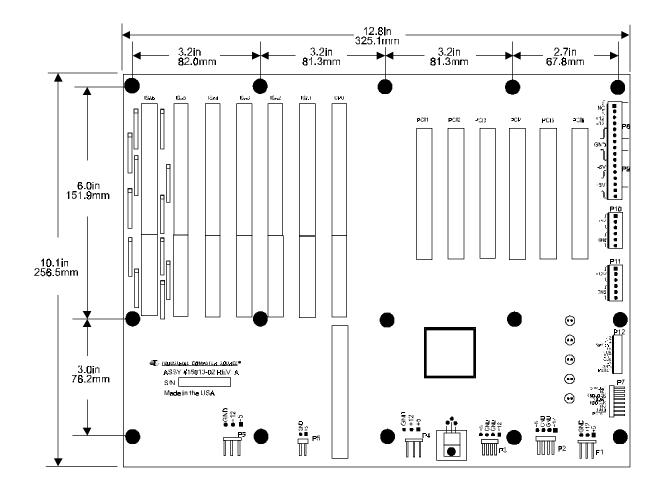

| 5 Slot Backplane, 15005-02                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |

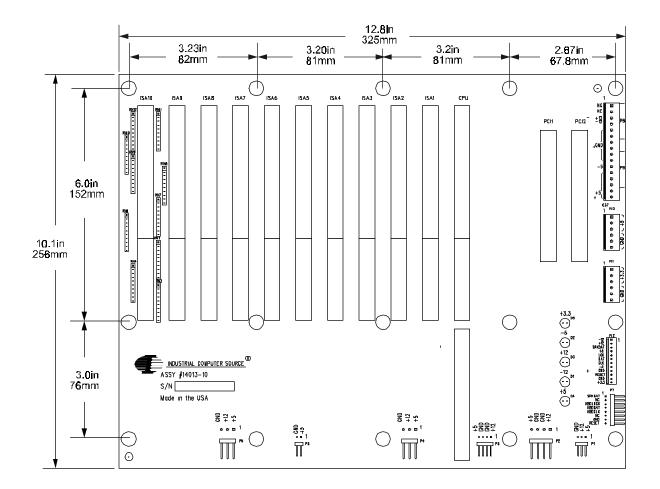

| 8 Slot Backplane, 15008-02 and 14008-02                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                 |

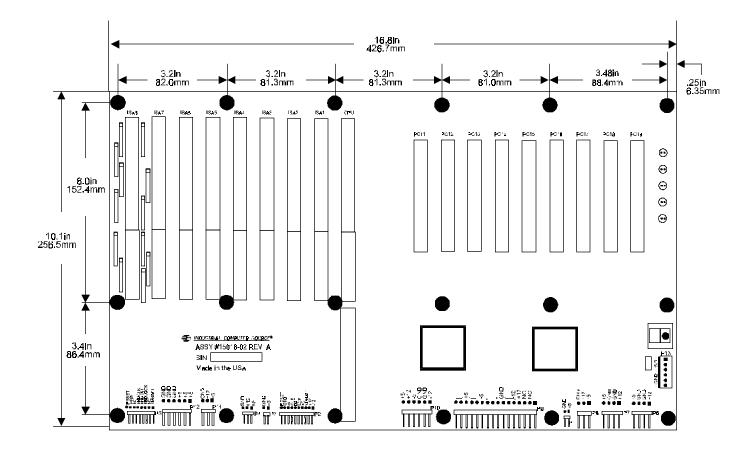

| 13 Slot Backplane, 15013-02 and 14013-02                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

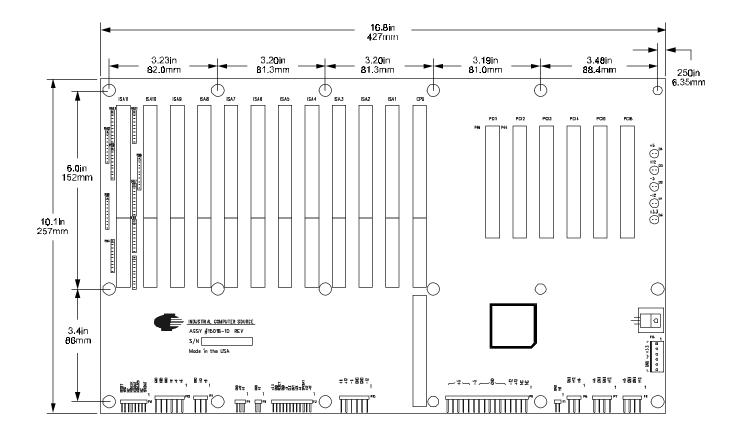

| 18 Slot Backplane, 15018-02 and 15018-10                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |

| Chapter 2: ISA Bus Overview                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-1                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |

| ISA Bus Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments                                                                                                                                                                                                                                                                                                                                                                             | 2-4<br>2-5<br>2-6                                                                                               |

| <ul> <li>XT (8 BIT) Bus Pin Assignments</li> <li>AT (16 BIT) Bus Extension Pin Assignments</li> <li>BUS Signals sorted by SIP Resistors</li> <li>Chapter 3: PCI Bus Overview</li> </ul>                                                                                                                                                                                                                                                                 | 2-4<br>2-5<br>2-6<br><b>3-1</b>                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors                                                                                                                                                                                                                                                                                                                                      | 2-4<br>2-5<br>2-6<br><b>3-1</b><br>3-1                                                                          |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br>Chapter 3: PCI Bus Overview<br>DEC Bridge Chip                                                                                                                                                                                                                                                                                    |                                                                                                                 |

| <ul> <li>XT (8 BIT) Bus Pin Assignments</li> <li>AT (16 BIT) Bus Extension Pin Assignments</li> <li>BUS Signals sorted by SIP Resistors</li> <li>Chapter 3: PCI Bus Overview</li> <li>DEC Bridge Chip</li> <li>PCI Signal Definitions</li> </ul>                                                                                                                                                                                                        |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups                                                                                                                                                                                                                          |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins                                                                                                                                                                                                           |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins                                                                                                                                                                                  |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins                                                                                                                                                        |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins<br>Arbitration Pins (Bus Masters only)                                                                                                                 |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins<br>Arbitration Pins (Bus Masters only)<br>Error Reporting Pins                                                                                         |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins<br>Arbitration Pins (Bus Masters only)<br>Error Reporting Pins<br>Interrupt Pins (Optional)                                  |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins<br>Arbitration Pins (Bus Masters only)<br>Error Reporting Pins<br>Interrupt Pins (Optional)<br>Cache Support Pins (Optional)                           |                                                                                                                 |

| XT (8 BIT) Bus Pin Assignments<br>AT (16 BIT) Bus Extension Pin Assignments<br>BUS Signals sorted by SIP Resistors<br><b>Chapter 3: PCI Bus Overview</b><br>DEC Bridge Chip<br>PCI Signal Definitions<br>PCI Signal Definitions<br>Pin Functional Groups<br>System Pins<br>Address and Data Pins<br>Interface Control Pins<br>Arbitration Pins (Bus Masters only)<br>Error Reporting Pins<br>Interrupt Pins (Optional)<br>Cache Support Pins (Optional) | 2-4<br>2-5<br>.2-6<br>3-1<br>3-1<br>3-1<br>.3-1<br>.3-2<br>.3-2<br>.3-2<br>.3-2<br>.3-3<br>.3-3<br>.3-3<br>.3-3 |

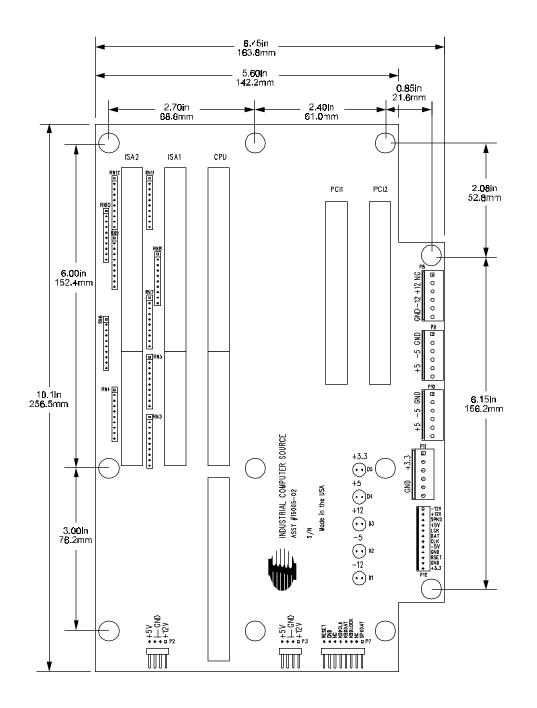

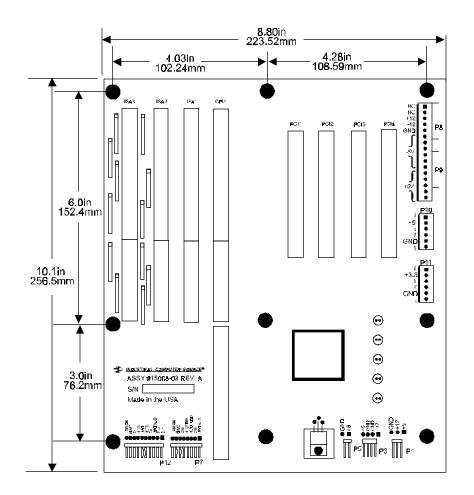

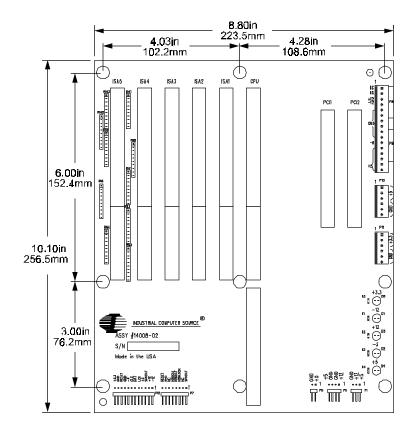

| Char  | oter 4 | : Dimensional | Drawings | 4 | 1 |

|-------|--------|---------------|----------|---|---|

| Cinap |        |               | Diamigo  |   | • |

## List of Figures

| 1-4 |

|-----|

| 1-5 |

| 1-5 |

| 3-2 |

| 3-6 |

| 4-2 |

| 4-3 |

| 4-4 |

| 4-5 |

| 4-6 |

| 4-7 |

| 4-8 |

|     |

## List of Tables

| Table 2-1: 32-bit PCI Connector Pinout 3-7 |

|--------------------------------------------|

|--------------------------------------------|

## **Current Revision 3A**

## July 1997

## **Chapter 1: Introduction**

#### Features

- 6 layer printed circuit board

- Extremely high EMI and RFI noise immunity

- Accept power connectors from standard PC bus power supplies

- Accepts CPU's with PCI Local Bus Extensions and standard ISA Bus CPU's

- Bus Power Check<sup>TM</sup> LED indicators for +3.3, +5, -5, +12, -12 VDC supplies

- Allows use of standard ISA Bus and PCI Local Bus option cards

- Bus terminating resistor sockets

Industrial Computer Source passive ISA/PCI backplanes are manufactured to the highest standards. They provide PCI Local Bus and ISA bus archietures to provide maximum flexibility in upgrage decisions. A standard ISA CPU may be installed in any ISA slot. A CPU with the PICMG compliant PCI Local Bus extension connector, installed in the ISA/PCI CPU slot, will provide full use of the PCI and ISA bus.

The DEC 21152 PCI-to-PCI bridge chip is incorporated into the design of the backplanes to overcome the PCI load limitations. The bridge chip adds a secondary PCI bus which operates independantly from the primary PCI bus, actually increasing overall performance in certain applications.

The backplane configurations are as follows:

15005-02 2/1/2Two ISA slots, one dedicated ISA/PCI CPU slot, and two PCI slots. 15008-02 3/1/4 Three ISA slots, one dedicated ISA/PCI CPU slot, and four PCI slots. One of the PCI slots is located on the Primary PCI bus and the other three are located on the secondary PCI Bus. 14008-02 5/1/2Five ISA slots, one dedicated ISA/PCI CPU slot, and two PCI slots. 15013-02 6/1/6 Six ISA slots, one dedicated ISA/PCI CPU slot, and six PCI slots. Two of the PCI slots are located on the Primary PCI bus and four are located on the secondary PCI Bus. 14013-10 10/1/2 Ten ISA slots, one dedicated ISA/PCI CPU slot, and two PCI slots. 15018-02 8/1/9 Eight ISA slots, one dedicated ISA/PCI CPU slot, and nine PCI slots. One of the PCI slots is located on the Primary PCI bus, four are located on the secondary PCI Bus, and four more are located on an additional secondary bus. 15018-10 11/1/6 Eleven ISA slots, one dedicated ISA/PCI CPU slot, and six PCI slots. One of the PCI slots is located on the Primary PCI bus, four are located on the secondary PCI Bus, and four more are located on an additional secondary bus PCI.

Each backplane is of a low capacitance design. This design minimizes signal crosstalk while keeping trace capacitance low which improves signal edges and rise and fall times. Each backplane also has a bank of LEDs to indicate the presence of the various power supply levels of the standard PC bus -  $\pm$ 5VDC,  $\pm$ 12VDC, and +3.3VDC. These LEDs provide a quick check of power supply operation without the need of a multimeter.

The Industrial Computer Source passive backplanes have been tested with a variety of plug-in CPU cards, from 8088 XT through Pentium and DEC Alpha systems. For applications involving option cards that are sensitive to bus impedance, termination SIPs are available as plug-ins to terminate the ISA bus of the backplane. Please refer to the section on Bus Termination for more detailed information.

## CAUTION!

Not all PCI cards work in all PCI slots in bridged backplanes. Some video cards cause bus contention when placed in certain PCI slots. This will cause fatal bus errors and potential damage to parts due to overheating. This problem can be avoided by placing your video card in Slot 2 for the 15013-02 backplane or Slot 1 on the 15008-02, 15018-2 backplanes, and 15018-10. Note that video cards that are PCI 2.1 compliant will not cause problems in a bridge chip environment.

## **Backplane Construction**

The ISA/PCI backplanes are constructed of 6 layers, with internal ground and power planes for RFI and EMI noise immunity and low trace capacitance. The signal traces are located on the outer layers (layers 1 and 6) and the inner layers (layers 3 and 4). The inner signal layers are used for clock and control signals. Layer 2 is the Ground plane and layer 5 is the Power plane.

### Connectors

Each backplane provides a 16-pin Molex-type connector for power input. A variety of auxiliary power and sense connectors are also provided for various chassis functions. Please see the Dimensional Drawings for pin assignments and orientations.

### **Input Power**

Each input is filtered by one or more large electrolytic capacitors for low frequency line noise rejection. Ceramic bypass filter capacitors of  $0.01\mu$ F improve noise immunity. All five input voltages have bypass capacitors.

Each power supply output is monitored by the exclusive Industrial Computer Source Bus Power Check<sup>™</sup> circuitry. A separate LED is lit by each supply voltage for a quick visible check of power supply operation. This is not, however, a tolerance verification. Troubleshooting requirements may require actual measurement of the power supply values to ensure operation to specified limits.

Note that troubleshooting a chassis may require a load on the power supply. Industrial Computer Source offers an optional ISA plug-in Power Supply Load Board that provides the minimum loading requirements of 0.96A load on +12VDC and 4A load on +5VDC. Please mention Model 10273-01B when ordering.

## **ISA BUS Termination**

Termination works as an impedance mismatch at the end of the bus, minimizing or preventing reflections and interference. If there is no termination, signals reach the end of the bus and reflect back down the bus. In extreme cases, the reflected signals can interfere with the real bus information, leading to spurious operation or lockups. This can become a significant factor as bus lengths and speeds increase. The applications most likely to be affected are telephony or other applications with many I/O boards drawing high current values off the +12V or -12V power connections.

Industrial Computer Source backplanes have supported 166MHz systems without bus termination and without problem. However, provision is made for installing terminations that might be required for your application.

Terminations connect the bus to +5VDC and ground, providing a path for the bus signals to dissipate. A terminated bus provides signals with less noise, although rise and fall times are slower. However, results are dependent on the CPU and option cards being used, and must be evaluated on a case-by-case basis.

There are three types of terminations that may be used; A Resistor Network; an RC Network; or a Diode Termination. A Resistor Network will provide the required impedance mismatch, but does result in loading. A RC Network does not impose a static load as a Resistor Network will, but it will affect the timing factors of the line to some degree. A Diode Termination is generally used in conjunction with a Resistor Network to reduce over- and under-shoot.

All Pentium and 486 vesa local or PCI CPU control signals that should never be terminated are as follows:

| A-1 (RES 12-3) | I/OCHCK |

|----------------|---------|

| B-8 (RES 12-7) | 0WS     |

| D-1 (RES 6-8)  | MEMCS16 |

| D-2 (RES 6-9)  | I/0CS16 |

| D-17 (RES 4-9) | MASTER  |

To end termination of a signal, simply cut the wire on the terminating resistor for the appropriate signal.

The backplanes provide termination sockets at the left end of the bus. These sockets accept standard 10-position SIPS manufactured by Bournes and others. Not all signal lines are available for termination. Refer to page 2-6 for the BUS signal information.

## **Resistor Termination**

The goal of termination resistors is to provide an impedance mismatch at the end of the bus to prevent signal reflections. This mismatch has to be balanced by the electrical capability of the CPU and option cards to drive the load imposed by the resistors.

Generally, terminations that connect to both +5V and ground work best, although terminations to +5V only are allowable.

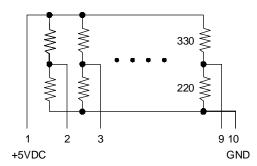

One way to provide terminations in digital systems is a resistor network connected to both +5V and ground. The following two examples represent such a resistor network in Single Inline Pin (SIP) form. Note that in both examples, the SIPs are inserted with pin 1 of the SIP toward the back of the chassis. While the following examples specify Bourns part numbers, equivalent values from other manufactures may be used. The following provides 330 ohms to +5V and 220 ohms to ground.

- Bourns part # 4610X-104-221/331 (Low profile)

- Bourns part #4610M-104-221/331 (Medium profile)

Figure 1-1: Resistor SIP Network

Reading the resistance from the signal pin of the SIP to either pin 1 or pin 10 will not provide the expected resistance of, for example, 220 or 330 ohms. This is because of the parallel resistance of the other paths. For example, the 220 ohms side will read 143 ohms (pin 10), and the 330 ohms side will read 156 ohms (pin 1). The actual values will change slightly because of allowed tolerance.

The following combination provides less bus loading than the first example and provides 330 ohms to +5 and 470 ohms to ground:

- Bourns part # 4610X-104-331/471 (Low profile)

- Bourns part #4610M-104-331/471 (Medium profile)

Other values are manufactured and can certainly be used if a problem persists on the bus. Not all cards behave well on large buses or in combination with other cards and may require some experimentation to completely isolate all intermittent operation. Turning the SIP around is allowed, even recommended occasionally, to better shape the signal being pulled high.

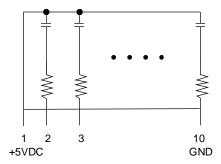

#### **RC Network Termination**

An alternative to a resistor network is an RC network. An RC network connects the signal lines through a resistor in series with a capacitor, to either +5V or ground. An advantage of an RC Network is that no static load is imposed on the bus, but increased capacitance on the line will affect timing factors. RC Networks are also slightly more expensive than Resistor Networks.

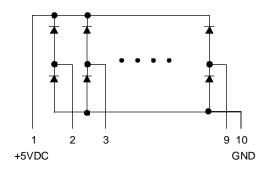

#### **DIODE Termination**

In some cases, diodes can be connected between the signal lines and both +5V and ground. Any spikes greater than the +5V rail are shunted and limited to +5V. Any negative spikes are shunted to ground. Thus, the bus sees only signals in the range of 0-5V. Diode termination reduces over- and under-shoot, but doesn't improve signal shape or edge times. Diode termination is generally used in conjunction with resistor termination.

Figure 1-2: RC SIP Network

Figure 1-3: Diode SIP Network

## Connectors

## 5 Slot Backplane, 15005-02

#### P2 - Drive Power Out Connector

4 pin single row, Amp 640457-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

### P3 - Drive Power Out Connector

4 pin single row, Amp 640457-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

## **P7-** CPU Connector

8 pin single row, Amp 640457-8

- 1 SPKDATA

- 2 N/C

- 3 KBDLOCK

- 4 KBDDAT

- 5 KBDCLK

- 6 N/C

- 7 GND

- 8 RESET

#### **P8/P9 - Power Supply Connector**

16 pin single row, Amp 1-640445-6

| 1  | N/C  | $(\mathbf{D}\mathbf{Q})$ |

|----|------|--------------------------|

| 1  | IN/C | (P8)                     |

| 2  | N/C  | (P8)                     |

| 3  | +12V | (P8)                     |

| 4  | -12V | (P8)                     |

| 5  | GND  | (P8)                     |

| 6  | GND  | (P8)                     |

| 7  | GND  |                          |

| 8  | GND  |                          |

| 9  | GND  | (P9)                     |

| 10 | GND  | (P9)                     |

| 11 | -5V  | (P9)                     |

| 12 | +5V  | (P9)                     |

| 13 | +5V  | (P9)                     |

| 14 | +5V  | (P9)                     |

| 15 | +5V  |                          |

| 16 | +5V  |                          |

### P10 - 5 Volt Power Connector

Unused: Not Populated

This connector is disabled on this board and should not be used.

#### P11 - 3.3 Volt Power Connector

6 pin single row, Amp 640445-6

| 1 | +3.3V |

|---|-------|

| 2 | +3.3V |

| 3 | +3.3V |

| 4 | GND   |

| 5 | GND   |

6 GND

#### P12 - Connection to CPU

10 pin single row, Amp 1-640457-0

- 1 -12V

- 2 +12V

- 3 SPKDATA

- 4 +5V

- 5 KBDLOCK

- 6 KBDDAT

- 7 KBDCLK

- 8 -5V

- 9 GND

- 10 RESET

- 11 GND

- 12 +3.3V

### 8 Slot Backplane, 15008-02 and 14008-02

| P1 - I/O Power Out             | P8/P9 - Power Supply Connector    |

|--------------------------------|-----------------------------------|

| 3 pin single row, Amp 640457-3 | 16 pin single row, Amp 1-640445-6 |

| 1 +5VDC                        | 1 N/C (P8)                        |

| 2 +12VDC                       | 2 N/C (P8)                        |

| 3 GND                          | 3 +12V (P8)                       |

|                                | 4 -12V (P8)                       |

| P3 - Drive Power Out Connector | 5 GND (P8)                        |

| 4 pin single row, Amp 640457-4 | 6 GND (P8)                        |

| 1 +12VDC                       | 7 GND                             |

| 2 GND                          | 8 GND                             |

| 3 GND                          | 9 GND (P9)                        |

| 4 +5VDC                        | 10 GND (P9)                       |

|                                | 11 -5V (P9)                       |

| P5- I/O Power Out Connector    | 12 +5V (P9)                       |

| 2 pin single row, Amp 640475-2 | 13 +5V (P9)                       |

|                                | 14 +5V (P9)                       |

| 1 +5VDC                        | 15 +5V                            |

| 2 GND                          | 16 +5V                            |

## **P7- CPU Connector**

8 pin single row, Amp 640457-8

- 1 SPKDATA

- 2 N/C

- 3 KBDLOCK

- 4 KBDDAT

- 5 KBDCLK

- 6 N/C

- 7 GND

- 8 RESET

### P10 - 5 Volt Power Connector

6 pin single row, Amp 640445-6

- 1 +5V

- 2 +5V

- 3 +5V

- 4 GND

- 5 GND

- 6 GND

#### P11 - 3.3 Volt Power Connector

6 pin single row, Amp 640445-6

| 1 10.01 |

|---------|

|         |

- 2 +3.3V

- 3 +3.3V

- 4 GND

- 5 GND

- 6 GND

#### P12 - Connection to CPU

10 pin single row, Amp 1-640457-0

- 1 -12V

- 2 +12V

- 3 SPKDATA

- 4 +5V

- 5 KBDLOCK

- 6 KBDDAT

- 7 KBDCLK

- 8 -5V

- 9 GND

- 10 RESET

- 11 GND

- 12 +3.3V

### 13 Slot Backplane, 15013-02 and 14013-02

#### P1 - I/O Power Out

3 pin single row, Amp 640457-3

- 1 +5VDC

- 2 +12VDC

- 3 GND

#### P2 - Drive Power Out Connector

4 pin single row, Amp 640389-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

#### P3 - Drive Power Out Connector

4 pin single row, Amp 640457-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

### P4 - I/O Power Out

3 pin single row, Amp 640389-3

- 1 +5VDC

- 2 +12VDC

- 3 GND

### P5- I/O Power Out Connector

2 pin single row, Amp 640457-2

- 1 +5VDC

- 2 GND

### P6 - I/O Power Out

3 pin single row, Amp 640389-3

1 +5VDC

- 2 +12VDC

- 3 GND

#### **P7-** CPU Connector

8 pin single row, Amp 640457-8

- 1 SPKDATA

- 2 N/C

- 3 KBDLOCK

- 4 KBDDAT

- 5 KBDCLK

- 6 N/C

- 7 GND

- 8 RESET

## **P8/P9 - Power Supply Connector**

16 pin single row, Amp 1-640445-6

| 1  | N/C  | (P8) |

|----|------|------|

| 2  | N/C  | (P8) |

| 3  | +12V | (P8) |

| 4  | -12V | (P8) |

| 5  | GND  | (P8) |

| 6  | GND  | (P8) |

| 7  | GND  |      |

| 8  | GND  |      |

| 9  | GND  | (P9) |

| 10 | GND  | (P9) |

| 11 | -5V  | (P9) |

| 12 | +5V  | (P9) |

| 13 | +5V  | (P9) |

| 14 | +5V  | (P9) |

| 15 | +5V  |      |

| 16 | +5V  |      |

## P10 - 5 Volt Power Connector

6 pin single row, Amp 640445-6

| 1 | +5V |

|---|-----|

| 2 | +5V |

| 3 | +5V |

| 4 | GND |

| 5 | GND |

6 GND

#### P11 - 3.3 Volt Power Connector

6 pin single row, Amp 640445-6

- 1 +3.3V

- 2 +3.3V

- 3 +3.3V

- 4 GND

- 5 GND

- 6 GND

#### P12 - Connection to CPU

10 pin single row, Amp 1-640456-0

- 1 -12V

- 2 +12V

- 3 SPKDATA

- 4 +5V

- 5 KBDLOCK

- 6 KBDDAT

- 7 KBDCLK

- 8 -5V

- 9 GND

- 10 RESET

- 11 GND

- 12 +3.3V

## 18 Slot Backplane, 15018-02 and 15018-10

#### P1- Remote Sense Connector

2 pin single row, Amp 640457-2

- 1 +5VDC

- 2 GND

#### P2 - Connection to CPU

10 pin single row, Amp 1-640457-0

- 1 -12V

- 2 +12V

- 3 SPKDATA

- 4 +5V

- 5 KBDLOCK

- 6 KBDDAT

- 7 KBDCLK

- 8 -5V

- 9 GND

- 10 RESET

- 11 GND

- 12 +3.3V

#### P3- Remote Sense Connector

2 pin single row, Amp 640457-2

- 1 +5VDC

- 2 GND

### P4 - I/O Power Out

3 pin single row, Amp 640457-3

- 1 +5VDC

- 2 +12VDC

- 3 GND

#### P5- Auxilary CPU Connector

8 pin single row, Amp 640457-8

- 1 SPKDATA

- 2 N/C

- 3 KBDLOCK

- 4 KBDDAT

- 5 KBDCLK

- 6 N/C

#### P5- Auxilary CPU Connector (cont)

- 7 GND

- 8 RESET

#### P6 - Drive Power Out Connector

4 pin single row, Amp 640389-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

#### **P7 - Drive Power Out Connector**

4 pin single row, Amp 640389-4

- 1 +12VDC

- 2 GND

- 3 GND

- 4 +5VDC

#### P8 - I/O Power Out

3 pin single row, Amp 640389-3

- 1 +5VDC

- 2 +12VDC

- 3 GND

#### **P9 - Power Supply Connector**

16 pin single row, Amp 1-640389-6

| 1  | N/C  | (P8) |

|----|------|------|

| 2  | N/C  | (P8) |

| 3  | +12V | (P8) |

| 4  | -12V | (P8) |

| 5  | GND  | (P8) |

| 6  | GND  | (P8) |

| 7  | GND  |      |

| 8  | GND  |      |

| 9  | GND  | (P9) |

| 10 | GND  | (P9) |

| 11 | -5V  | (P9) |

| 12 | +5V  | (P9) |

| 13 | +5V  | (P9) |

| 14 | +5V  | (P9) |

| 15 | +5V  |      |

|    |      |      |

16 + 5V

#### P10 - Power Supply Connector

6 pin single row, Amp 640389-6

- 1 -12V

- 2 GND

- 3 GND

- 4 -5V

- 5 +12V

- 6 +5V

#### P11 - I/O Power Out

3 pin single row, Amp 640389-3

- 1 +5VDC

- 2 +12VDC

- 3 GND

#### P12 - 5 Volt Power Connector

6 pin single row, Amp 640389-6

| 1 | +5V |

|---|-----|

| 2 | +5V |

| 3 | +5V |

| 4 | GND |

5 GND

6 GND

#### P13 - 3.3 Volt Power Connector

6 pin single row, Amp 640445-6

| 1 | +3.3V |

|---|-------|

| 2 | +3.3V |

| 3 | +3.3V |

| 4 | GND   |

| 5 | GND   |

| 6 | GND   |

This page intentionally left blank.

## **Chapter 2: ISA Bus Overview**

## **ISA Bus Signal Descriptions**

The following is a description of the ISA Bus signals. All signal lines are TTL-compatible. A # symbol at the end of a signal name indicates that the active state occurs when the signal is at a low voltage. When the # symbol is absent, the signal is active at a high voltage.

- AEN Address Enable is used to degate the microprocessor and other devices from the I/O channel to allow DMA transfers to take place. When this line is active, the DMA controller has control of the address bus, the data-bus Read command lines (memory and I/O), and the Write command lines (memory and I/O).

- BALE Address Latch Enable (BALE) is provided by the bus controller and is used on the system board to latch valid addresses and memory decodes from the microprocessor. It is available to the I/O channel as an indicator of a valid microprocessor or DMA address (when used with AEN). Microprocessor addresses SA[19..0] are latched with the falling edge of BALE. BALE is forced high during DMA cycles.

- CLK CLK is the system clock. The clock has a 50% duty cycle. This signal should only be used for synchronization. It is not intended for uses requiring a fixed frequency.

- DACK[7..5]#, DACK[3..0]#

DMA Acknowledge DACK[7..5]# and DACK[3..0]# are used to acknowledge DMA requests DRQ[7..5] and DRQ[3..0]. They are active low.

DRQ[7..5], DRQ[3..0]

DMA Requests DRQ[7..5] and DRQ[3..0] are asynchronous channel requests used by peripheral devices and the I/O channel microprocessors to gain DMA service (or control of the system). They are prioritized, with DRQ0 having the highest priority and DRQ7 having the lowest. A request is generated by bringing a DRQ line to an active level. A DRQ line must be held high until the corresponding DMA Request Acknowledge (DACK) line goes active. DRQ[3..0] will perform 8-bit DMA transfers; DRQ[7..5] will perform 16-bit transfers.

- I/O CHRDY I/O Channel Ready is pulled low by a memory or I/O device to lengthen I/O or memory cycles. Any slow device using this line should drive it low immediately upon detecting its valid address and a Read or Write command. Machine cycles are extended by an integral number of clock cycles. This signal should be held low for no more than 2.5 microseconds.

- IOCHK# I/O Channel Check provides the system board with parity information about memory or devices on the I/O channel. When this signal is active, it indicates an uncorrectable system error.

- IOCS16#I/O 16 Chip Select signals the system board that the present data transfer is a 16-<br/>bit, 1 wait-state, I/O cycle. It is derived from an address decode. IOCS16# is active<br/>low and should be driven with an open collector or tri-state driver capable of sinking<br/>20mA.

- IOR# I/O Read instructs an I/O device to read the data in the data bus. It may be driven by the system microprocessor or DMA controller, or by a microprocessor or DMA controller resident on the I/O channel. This signal is active low.

- IOW# I/O Write instructs an I/O device to drive its data onto the data bus. It may be driven by any microprocessor or DMA controller in the system. This signal is active low.

#### IRQ[15,14], IRQ[12..9], IRQ[7..3]

Interrupt Requests are used to signal the microprocessor that an I/O device needs attention. The interrupt requests are prioritized, with IRQ[15..14] and IRQ[12..9] having the highest priority (IRQ9 is the highest) and IRQ[7..3] having the lowest priority (IRQ7 is the lowest). An interrupt request is generated when an IRQ line is raised from low to high. The line must be held high until the microprocessor acknowledges the interrupt request (Interrupt Service routine).

- LA[23..17] These signals (unlatched) are used to address memory and I/O devices within the system. They give the system up to 16MB of addressability. These signals are valid when BALE is high. LA[23..17] are not latched during microprocessor cycles and therefore do not stay valid for the whole cycle. Their purpose is to generate memory decodes for 1 wait-state memory cycles. These decodes should be latched by I/O adapters on the falling edge of BALE. These signals also may be driven by other microprocessors or DMA controllers that reside on the I/O channel.

- Master# Master# is used with a DRQ line to gain control of the system. A processor or DMA controller on the I/O channel may issue a DRQ to a DMA channel in cascade mode and receive a DACK#. Upon receiving the DACK#, an I/O microprocessor may pull Master# low, which will allow it to control the system address, data, and control lines (a condition known as tri-state). After Master# is low, the I/O microprocessor must wait one system clock period before driving the address and data lines, and two clock periods before issuing a Read or Write command. If this signal is held low for more than 15 microseconds, system memory may be lost because of a lack of refresh.

- MEMCS16# M16# Chip Select signals the system board if the present data transfer is a 1 waitstate, 16-bit, memory cycle. It must be derived from the decode of LA[23..17]. MEMCS16# should be driven with an open collector or tri-state driver capable of sinking 20mA.

- 0WS# The Zero Wait State (0WS#) signal tells the microprocessor that it can complete the present bus cycle without inserting any additional wait cycles. In order to run a memory cycle to a 16-bit device without wait cycles, 0WS# is derived from an address decode gated with a Read or Write command. In order to run a memory cycle to an 8-bit device with a minimum of two wait states, 0WS# should be driven active on system clock after the Read or Write command is active gated with the address decode for the device. Memory Read and Write commands to a 8-bit device are active on the falling edge of the system clock. 0WS# is active low and should be driven with an open collector or tri-state driver capable of sinking 20mA.

- OSC Oscillator (OSC) is a high-speed clock with a 70-nanosecond period (14.31818 MHz). This signal is not synchronous with the system clock. It has a 50% duty cycle.

- REFRESH# The REFRESH# signal is used to indicate a refresh cycle and can be driven by a microprocessor on the I/O channel.

- RESET Reset is used to reset or initialize system logic at power-up time or during a low linevoltage outage. This signal is active high.

- SA[19..0] Address bits SA[19..0] are used to address memory and I/O devices within the system. These twenty address lines, in addition to LA[23..17], allow access of up to 16MB of memory. SA[19..0] are gated on the system bus when BALE is high and are latched in the falling edge of BALE. These signals are generated by the microprocessors or DMA Controller. They also may be driven by other microprocessors or DMA controllers that reside in the I/O channel.

- SBHE# System Bus High Enable (SBHE#) indicates a transfer of data on the upper byte of the data bus, SD[15..8]. 16-bit devices use SBHE# to condition data bus buffers tied to SD[15..8].

- SD[15..0] Data signals SD[15..0] provide bus bits 15 through 0 for the microprocessor, memory, and I/O devices. SD15 is the most-significant bit and SD0 is the leastsignificant bit. All 8-bit devices on the I/O channel should use SD[7..0] for communications to the microprocessor. The 16-bit devices will use SD[15..0]. To support 8-bit devices, the data on SD[15..8] will be gated to SD[7..0] during 8-bit transfers to these devices. 16-bit microprocessor transfers to 8-bit devices will be converted to two 8-bit transfers.

#### SMEMR#, MRMR#

These signals instruct the memory devices to drive data onto the data bus. SMEMR# is active only when the memory decode is within the low 1MB of memory space. MRMR# is active on all memory read cycles. MRMR# may be driven by any microprocessor or DMA controller in the system. SMEMR# is derived from MRMR# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MRMR#, it must have the address lines valid on the bus for one system clock period before driving MRMR# active. Both signals are active low.

#### SMEMW#, MEMW#

These signals instruct the memory devices to store the data present on the data bus. SMEMW# is active only when the memory decode is within the low 1MB of the memory space. MEMW# is active on all memory write cycles. MEMW# may be driven by any microprocessor or DMA controller in the system. SMEMW# is derived from MEMW# and the decode of the low 1MB of memory. When a microprocessor on the I/O channel wishes to drive MEMW#, it must have the address lines valid on the bus for one system clock period before driving MEMW# active. Both signals are active low.

T/C Terminal Count (T/C) provides a pulse when the terminal count for any DMA channel is reached.

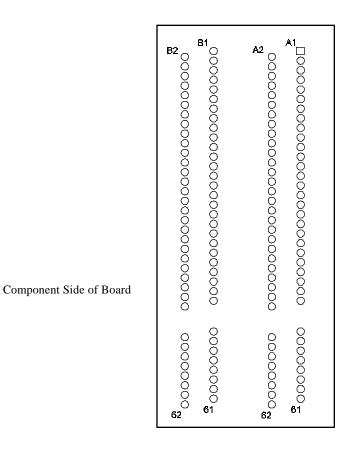

## XT (8 BIT) Bus Pin Assignments

| Solder Side of Option Board |      |            |             |

|-----------------------------|------|------------|-------------|

| <b>Description</b>          | Res  | <u>Pin</u> | <u>Side</u> |

| Ground                      | NC   | 1          | В           |

| Reset                       | 4.7K | 2          | В           |

| +5 Volts                    | NC   | 3          | В           |

| IRQ2 or 9                   | NC   | 4          | В           |

| -5 Volts                    | NC   | 5          | В           |

| DRQ2                        | NC   | 6          | В           |

| -12 Volts                   | NC   | 7          | В           |

| 0WS#                        | 12-7 | 8          | В           |

| +12 Volts                   | NC   | 9          | В           |

| Ground                      | NC   | 10         | В           |

| SMEMW#                      | 9-2  | 11         | В           |

| SMEMR#                      | 9-3  | 12         | В           |

| IOW#                        | 9-4  | 13         | В           |

| IOR#                        | 9-5  | 14         | В           |

| DACK3#                      | 9-6  | 15         | В           |

| DRQ3                        | NC   | 16         | В           |

| DACK1#                      | 9-7  | 17         | В           |

| DRQ1                        | NC   | 18         | В           |

| REFRESH#                    | 9-8  | 19         | В           |

| CLK                         | 9-9  | 20         | В           |

| IRQ7                        | NC   | 21         | В           |

| IRQ6                        | NC   | 22         | В           |

| IRQ5                        | NC   | 23         | В           |

| IRQ4                        | NC   | 24         | В           |

| IRQ3                        | NC   | 25         | В           |

| DACK2#                      | 6-2  | 26         | В           |

| T/C                         | 6-3  | 27         | В           |

| BALE                        | 6-4  | 28         | В           |

| +5 Volts                    | NC   | 29         | В           |

| OSC                         | 6-5  | 30         | В           |

| Ground                      | NC   | 31         | В           |

| Component side of Option Board |            |      |                    |

|--------------------------------|------------|------|--------------------|

| <u>Side</u>                    | <u>Pin</u> | Res  | <b>Description</b> |

| А                              | 1          | 12-2 | I/OCHK#            |

| А                              | 2          | 11-2 | SD7                |

| А                              | 3          | 11-3 | SD6                |

| А                              | 4          | 11-4 | SD5                |

| А                              | 5          | 11-5 | SD4                |

| А                              | 6          | 11-6 | SD3                |

| А                              | 7          | 11-7 | SD2                |

| А                              | 8          | 11-8 | SD1                |

| А                              | 9          | 11-9 | SD0                |

| А                              | 10         | NC   | I/OCHRDY           |

| А                              | 11         | 12-9 | AEN                |

| А                              | 12         | 10-6 | SA19               |

| А                              | 13         | 10-7 | SA18               |

| А                              | 14         | 10-8 | SA17               |

| А                              | 15         | 10-9 | SA16               |

| А                              | 16         | 8-2  | SA15               |

| А                              | 17         | 8-3  | SA14               |

| А                              | 18         | 8-4  | SA13               |

| А                              | 19         | 8-5  | SA12               |

| А                              | 20         | 8-6  | SA11               |

| А                              | 21         | 8-7  | SA10               |

| А                              | 22         | 8-8  | SA9                |

| А                              | 23         | 8-9  | SA8                |

| А                              | 24         | 7-2  | SA7                |

| А                              | 25         | 7-3  | SA6                |

| А                              | 26         | 7-4  | SA5                |

| А                              | 27         | 7-5  | SA4                |

| А                              | 28         | 7-6  | SA3                |

| А                              | 29         | 7-7  | SA2                |

| А                              | 30         | 7-8  | SA1                |

| А                              | 31         | 7-9  | SA0                |

Note:

Pin B4 is IRQ2 for an XT

Pin B4 is IRQ9 for an AT which is redirected as IRQ2

\* -REFRESH is -DACK0 on an XT 8-bit system.

## AT (16 BIT) Bus Extension Pin Assignments

| Solder Side of Option Board |     |            |             |

|-----------------------------|-----|------------|-------------|

| Description                 | Res | <u>Pin</u> | <u>Side</u> |

| MEMCS16#                    | 6-8 | 1          | D           |

| I/OCS16#                    | 6-9 | 2          | D           |

| IRQ10                       | NC  | 3          | D           |

| IRQ11                       | NC  | 4          | D           |

| IRQ12                       | NC  | 5          | D           |

| IRQ15                       | NC  | 6          | D           |

| IRQ14                       | NC  | 7          | D           |

| DACK0#                      | 4-2 | 8          | D           |

| DRQ0#                       | NC  | 9          | D           |

| DACK5#                      | 4-5 | 10         | D           |

| DRQ5                        | NC  | 11         | D           |

| DACK6#                      | 4-7 | 12         | D           |

| DRQ6#                       | NC  | 13         | D           |

| DACK7#                      | 4-8 | 14         | D           |

| DRQ7                        | NC  | 15         | D           |

| 5VDC                        | NC  | 16         | D           |

| MASTER#                     | 4-9 | 17         | D           |

| GROUND                      | NC  | 18         | D           |

| Component Side of Option Board |            |     |             |

|--------------------------------|------------|-----|-------------|

| <u>Side</u>                    | <u>Pin</u> | Res | Description |

| С                              | 1          | 6-7 | SBHE#       |

| С                              | 2          | 5-3 | LA23        |

| С                              | 3          | 5-4 | LA22        |

| С                              | 4          | 5-5 | LA21        |

| С                              | 5          | 5-6 | LA20        |

| С                              | 6          | 5-7 | LA19        |

| С                              | 7          | 5-8 | LA18        |

| С                              | 8          | 5-9 | LA17        |

| С                              | 9          | 4-4 | MRMR#       |

| С                              | 10         | 4-6 | MEMW#       |

| С                              | 11         | 3-2 | SD08        |

| С                              | 12         | 3-3 | SD09        |

| С                              | 13         | 3-4 | SD10        |

| С                              | 14         | 3-5 | SD11        |

| С                              | 15         | 3-6 | SD12        |

| С                              | 16         | 3-7 | SD13        |

| С                              | 17         | 3-8 | SD14        |

| С                              | 18         | 3-9 | SD15        |

## **BUS Signals sorted by SIP Resistors**

| C<br>C<br>C | 11<br>12 | RN3-1<br>RN3-2 | +5V     |

|-------------|----------|----------------|---------|

| С           |          | RN3-2          |         |

|             | 12       | 1              | SD08    |

| C           |          | RN3-3          | SD09    |

| C           | 13       | RN3-4          | SD10    |

| С           | 14       | RN3-5          | SD11    |

| С           | 15       | RN3-6          | SD12    |

| С           | 16       | RN3-7          | SD13    |

| С           | 17       | RN3-8          | SD14    |

| С           | 18       | RN3-9          | SD15    |

|             |          | RN3-10         | GND     |

|             |          |                |         |

|             |          | RN4-1          | +5V     |

| D           | 8        | RN4-2          | DACK0#  |

|             |          | RN4-3          | NC      |

| С           | 9        | RN4-4          | MRMC#   |

| D           | 10       | RN4-5          | DACK5#  |

| С           | 10       | RN4-6          | MEMW#   |

| D           | 12       | RN4-7          | DACK6#  |

| D           | 14       | RN4-8          | DACK7#  |

| D           | 17       | RN4-9          | MASTER# |

|             |          | RN4-10         | GND     |

|             |          |                |         |

|             |          | RN5-1          | +5V     |

|             |          | RN5-2          | NC      |

| С           | 2        | RN5-3          | LA23    |

| С           | 3        | RN5-4          | LA22    |

| С           | 4        | RN5-5          | LA21    |

| С           | 5        | RN5-6          | LA20    |

| С           | 6        | RN5-7          | LA19    |

| С           | 7        | RN5-8          | LA18    |

| С           | 8        | RN5-9          | LA17    |

|             |          | RN5-10         | GND     |

| Side | Pin | Res/Pin | Description |

|------|-----|---------|-------------|

|      |     | RN6-1   | +5V         |

| В    | 26  | RN6-2   | DACK2#      |

| В    | 27  | RN6-3   | T-C         |

| В    | 28  | RN6-4   | BALE        |

| В    | 30  | RN6-5   | OSC         |

|      |     | RN6-6   | NC          |

| С    | 1   | RN6-7   | SBHE#       |

| D    | 1   | RN6-8   | MEMCS16#    |

| D    | 2   | RN6-9   | I/O16#      |

|      |     | RN6-10  | GND         |

|      |     |         |             |

|      |     | RN7-1   | +5V         |

| А    | 24  | RN7-2   | SA7         |

| А    | 25  | RN7-3   | SA6         |

| А    | 26  | RN7-4   | SA5         |

| А    | 27  | RN7-5   | SA4         |

| А    | 28  | RN7-6   | SA3         |

| А    | 29  | RN7-7   | SA2         |

| А    | 30  | RN7-8   | SA1         |

| А    | 31  | RN7-9   | SA0         |

|      |     | RN7-10  | GND         |

|      |     |         |             |

|      |     | RN8-1   | +5V         |

| А    | 16  | RN8-2   | SA15        |

| А    | 17  | RN8-3   | SA14        |

| А    | 18  | RN8-4   | SA13        |

| А    | 19  | RN8-5   | SA12        |

| А    | 20  | RN8-6   | SA11        |

| А    | 21  | RN8-7   | SA10        |

| А    | 22  | RN8-8   | SA9         |

| А    | 23  | RN8-9   | SA8         |

|      |     | RN8-10  | GND         |

## BUS Signals sorted by SIP Resistors (cont)

| Side | Pin | Res/Pin | Description |

|------|-----|---------|-------------|

|      |     | RN9-1   | +5V         |

| В    | 11  | RN9-2   | SMEMW#      |

| В    | 12  | RN9-3   | SMEMR#      |

| В    | 13  | RN9-4   | IOW#        |

| В    | 14  | RN9-5   | IOR#        |

| В    | 15  | RN9-6   | DACK3#      |

| В    | 17  | RN9-7   | DACK1#      |

| В    | 19  | RN9-8   | REFRESH#    |

| В    | 20  | RN9-9   | CLK         |

|      |     | RN9-10  | GND         |

|      |     |         |             |

|      |     | RN10-1  | +5V         |

|      |     | RN10-2  | NC          |

|      |     | RN10-3  | NC          |

|      |     | RN10-4  | NC          |

|      |     | RN10-5  | NC          |

| А    | 12  | RN10-6  | SA19        |

| А    | 13  | RN10-7  | SA18        |

| А    | 14  | RN10-8  | SA17        |

| А    | 15  | RN10-9  | SA16        |

|      |     | RN10-1  | GND         |

| Side | Pin | Res/Pin | Description |

|------|-----|---------|-------------|

|      |     | RN11-1  | +5V         |

| А    | 2   | RN11-2  | SD7         |

| А    | 3   | RN11-3  | SD6         |

| А    | 4   | RN11-4  | SD5         |

| А    | 5   | RN11-5  | SD4         |

| А    | 6   | RN11-6  | SD3         |

| А    | 7   | RN11-7  | SD2         |

| А    | 8   | RN11-8  | SD1         |

| А    | 9   | RN11-9  | SD0         |

|      |     | RN11-10 | GND         |

|      |     |         |             |

|      |     | RN12-1  | +5V         |

| А    | 1   | RN12-2  | I/OCHK#     |

|      |     | RN12-3  | NC          |

|      |     | RN12-4  | NC          |

|      |     | RN12-5  | NC          |

|      |     | RN12-6  | NC          |

| В    | 8   | RN12-7  | 0WS#        |

|      |     | RN12-8  | NC          |

| А    | 11  | RN12-9  | AEN         |

|      |     | RN12-10 | GND         |

This page intentionally left blank

## **Chapter 3: PCI Bus Overview**

The PCI Local Bus is a high performance, 32-bit or 64-bit bus with multiplexed address and data lines. It is intended for use as an interconnect mechanism between highly integrated peripheral controller components, peripheral add-in boards, and processor/memory systems.

The PCI component and add-in card interface is processor independent, enabling an efficient transition to future processor architectures. Processor independence allows the PCI Local Bus to be optimized for I/O functions, enables concurrent operation of the local bus with the processor/ memory subsystem, and accommodates high performance peripherals in addition to graphics. Movement to enhanced video and multimedia displays and other high bandwidth I/O will continue to increase local bus bandwidth requirements. A transparent 64-bit extension of the 32-bit data and address buses is defined, doubling the bus bandwidth and offering forward and backwards compatibility of 32-bit and 64-bit PCI Local Bus peripherals.

The PCI Local Bus standard offers additional benefits to the users of PCI based systems. Configuration registers are specified for PCI components and add-in cards. A system with embedded auto configuration software offers true ease-of-use for the system user by automatically configuring PCI add-in cards at power on.

## **DEC Bridge Chip**

The DEC bridge chip is a high-performance chip that expands the electrical capacity of all PCI systems. The bridge chip allows more PCI devices than a single PCI bus can support. The bridge chip has two PCI interfaces. The primary PCI interface connects directly to the PCI bus closest to the host CPU. The secondary PCI interface creates a new and independent PCI bus. The primary function of the bridge is to allow transactions to occur between a master on one PCI bus and a target on the other PCI bus.

The bridge chip also allows the two PCI buses to operate independently. A master and a target located on the same PCI bus can communicate with each other even if the other PCI bus is busy. As a result, the bridge can isolate traffic between devices on one PCI bus from devices on other PCI buses. This is a major benefit to system performance in some applications such as multimedia.

The bridge chip can extend a system beyond the electrical loading limits of a single PCI bus. Each new PCI bus created by the addition of a bridge chip provides support for additional electrical loads.

## **PCI Signal Definitions**

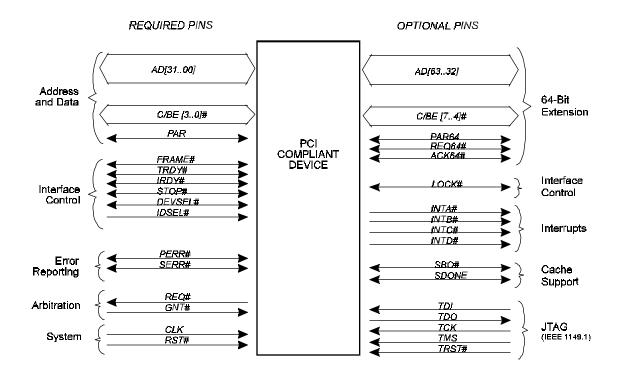

The PCI interface requires a minimum of 47 pins for a target-only device and 49 pins for a master to handle data and addressing, interface control, arbitration, and system functions. Figure 2-1 shows the pins in functional groups, with required pins on the left side and optional pins on the right side. The direction indicator on signals in Figure 2-1 assumes a combination master/target device.

Figure 2-1: PCI Signals

## **Pin Functional Groups**

The PCI pin definitions are organized in the functional groups shown in Figure 2-1. A # symbol at the end of a signal name indicates that the active state occurs when the signal is at a low voltage. When the # symbol is absent, the signal is active at a high voltage.

#### **System Pins**

- CLK Clock provides timing for all transactions on PCI and is an input to every PCI device.

- RST# Reset is used to bring PCI specific registers, sequencers, and signals to a consistent state.

#### Address and Data Pins

- AD[31..00] Address and Data are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. PCI supports both read and write bursts.

- C/BE [3..0]# Bus Commands and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, these pins define the bus command; during the data phase they are used as byte enables. The byte enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE0# applies to byte 0 (lsb) and C/BE3# applies to byte 3 (msb).

PAR Parity is even parity across AD[31..00] and C/BE[3..0]#. Parity generation is required by all PCI agents. The master drives PAR for address and write data phases; the target drives PAR for read data phases.

#### **Interface Control Pins**